# Memory Checking for Parallel RAMs

Surya Mathialagan MIT

• We define a new notion of **memory checking** in the **parallel RAM** model.

#### Quick Overview

- We define a new notion of **memory checking** in the **parallel RAM** model.

We construct memory checkers for PRAMs matching the <u>asymptotic efficiency</u> of memory checkers for the RAM setting, while achieving optimal parallel depth.

#### Quick Overview

- We define a new notion of memory checking in the parallel RAM model.

- polylog overhead.

• We construct memory checkers for PRAMs matching the <u>asymptotic efficiency</u> of memory checkers for the RAM setting, while <u>achieving optimal parallel depth</u>.

As an application, we construct maliciously secure Oblivious Parallel RAM with

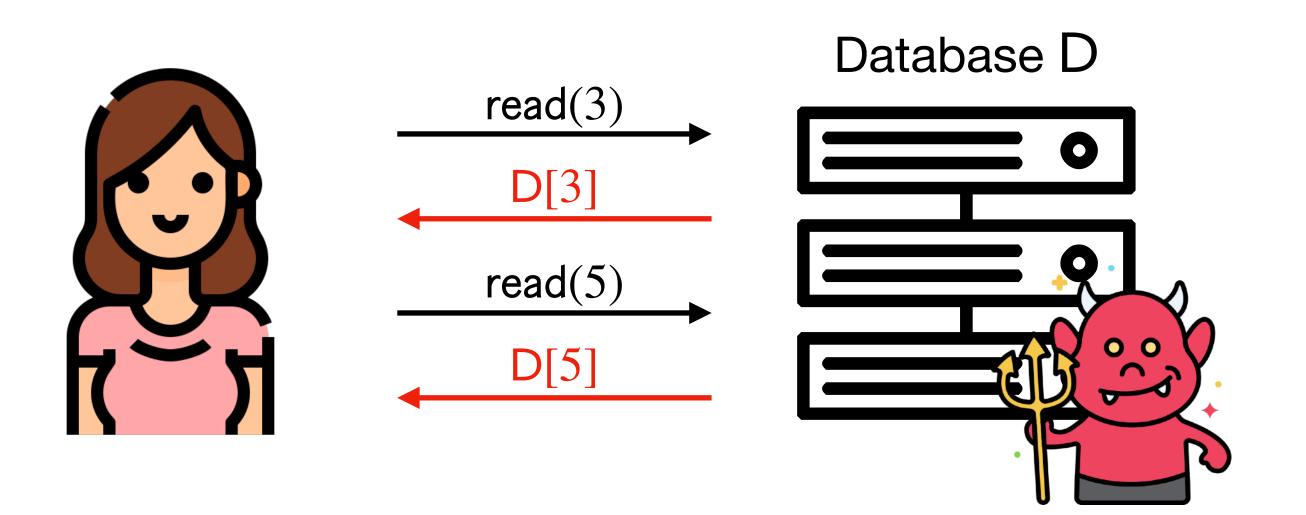

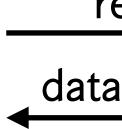

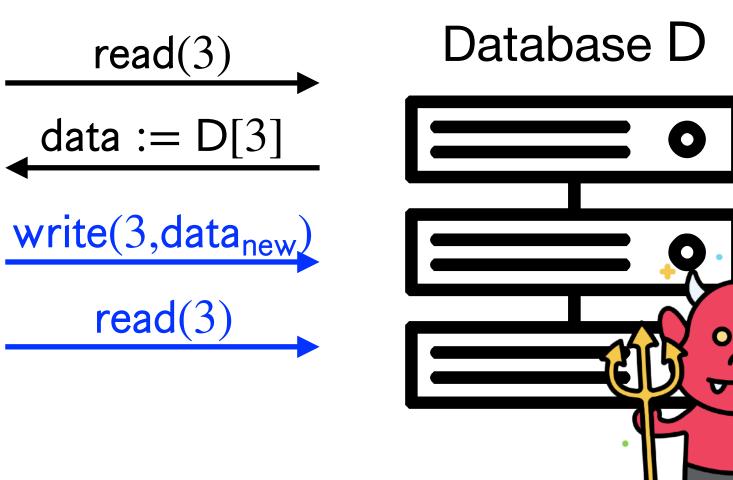

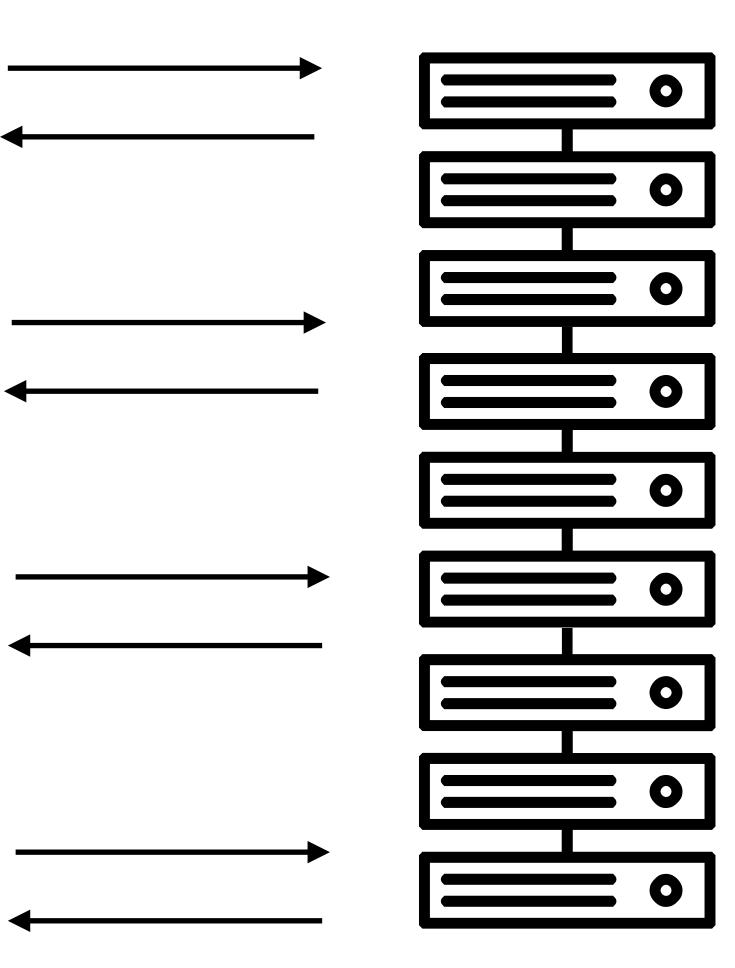

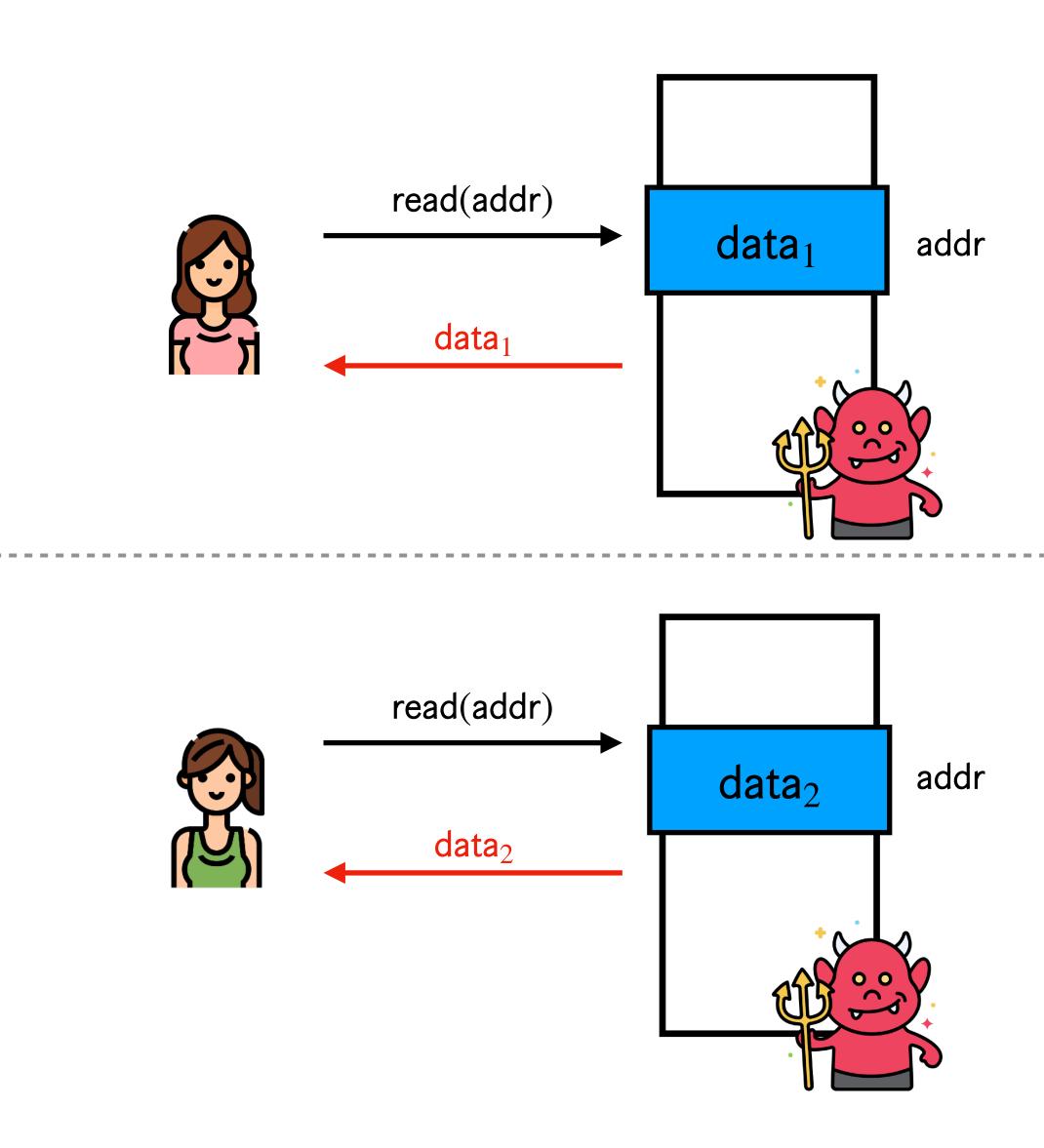

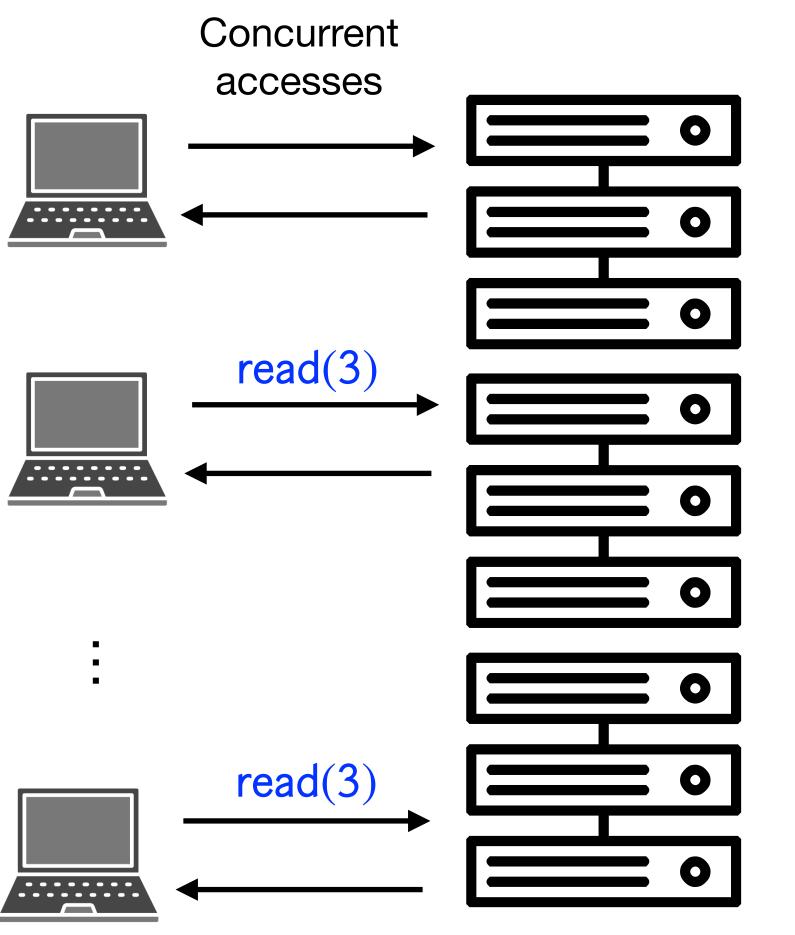

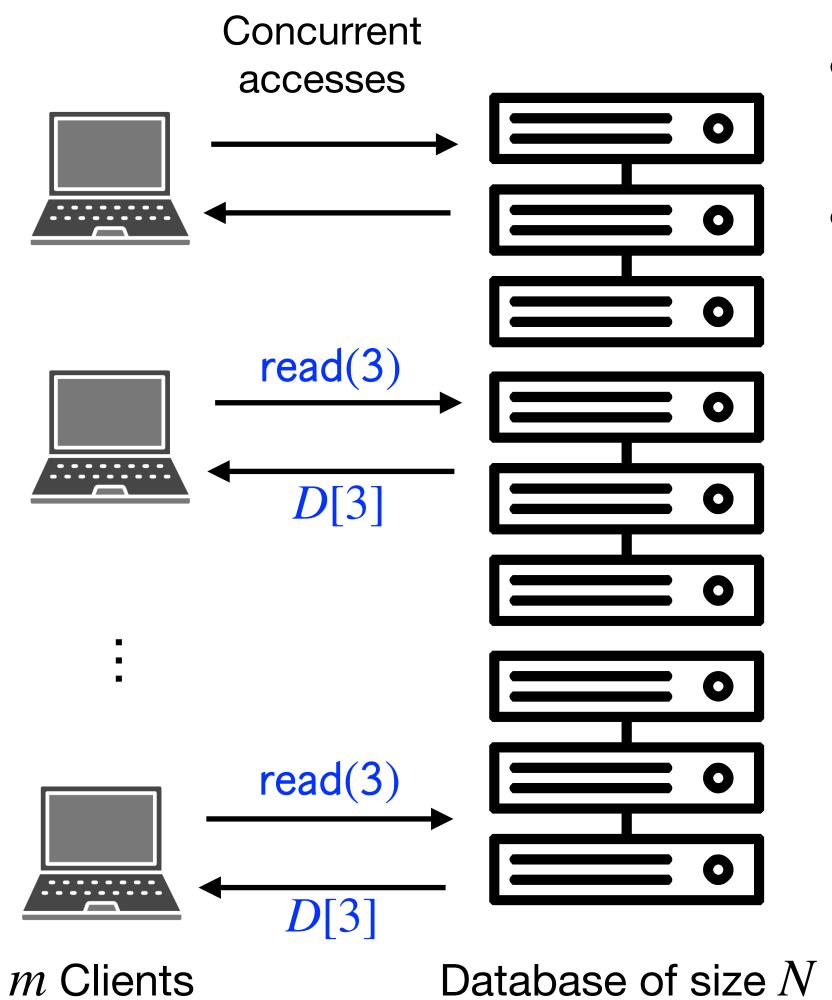

read(3)

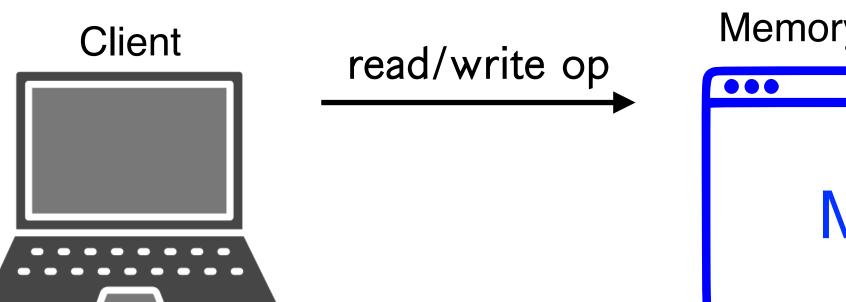

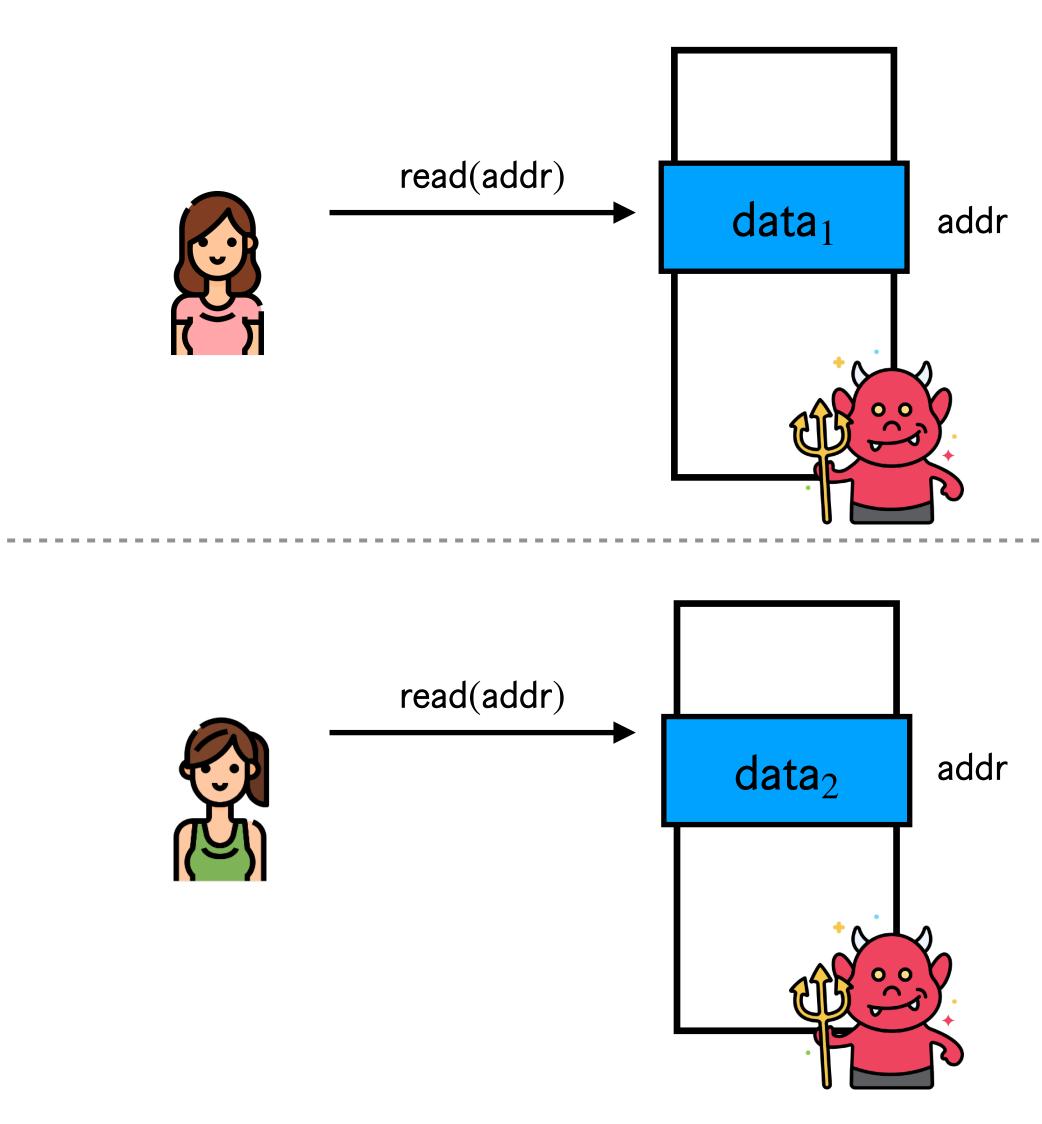

server is sending back correct responses?

How can a client use her small but trusted local memory to ensure that

- server is sending back correct responses?

- Answer: Authentication

How can a client use her small but trusted local memory to ensure that

- server is sending back correct responses?

- Answer: Authentication... if the database is static

How can a client use her small but trusted local memory to ensure that

• What if the database contents are dynamically updated?

write(3,datanew)

What if the database contents are dynamically updated?

What if the database contents are dynamically updated?

- What if the database contents are dynamically updated?

- We want reads to correspond to most recent version! (i.e. datanew not data)

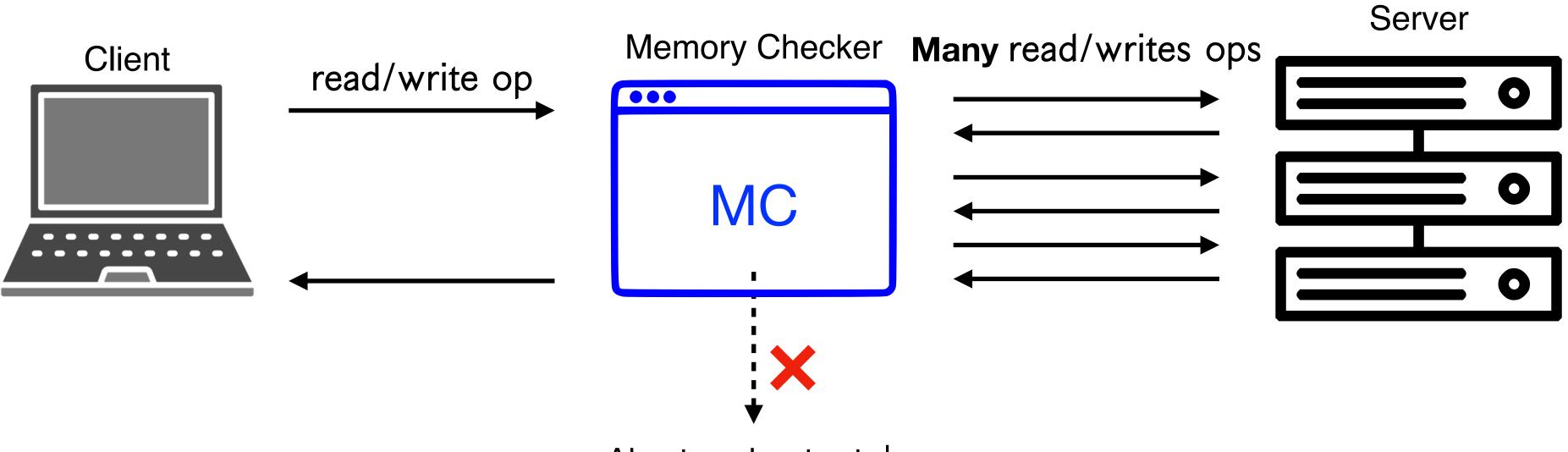

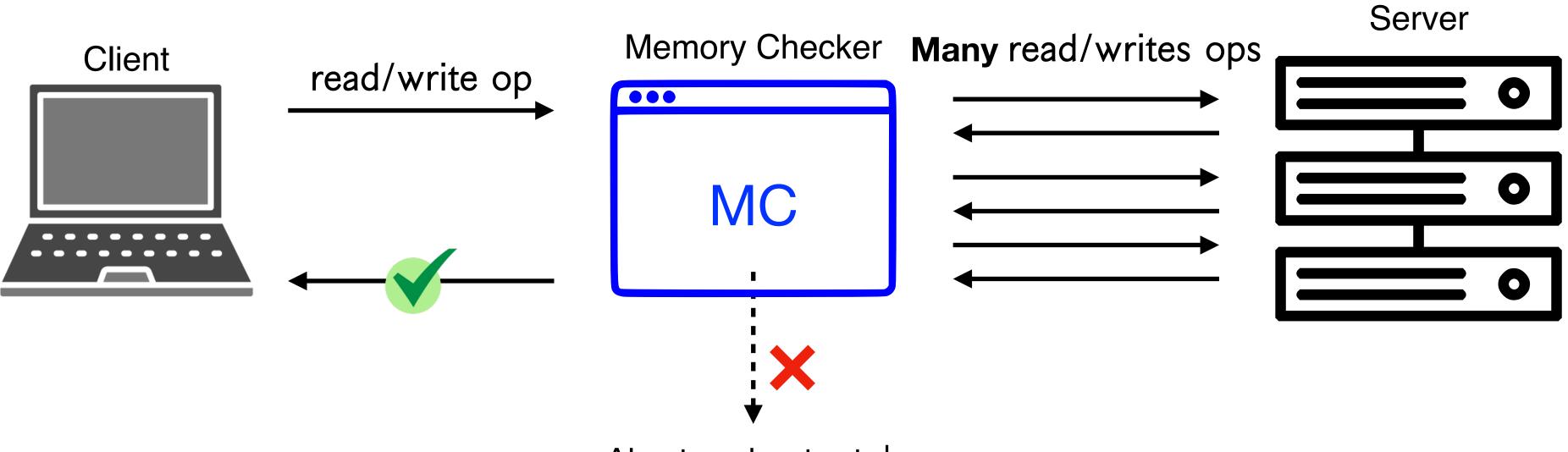

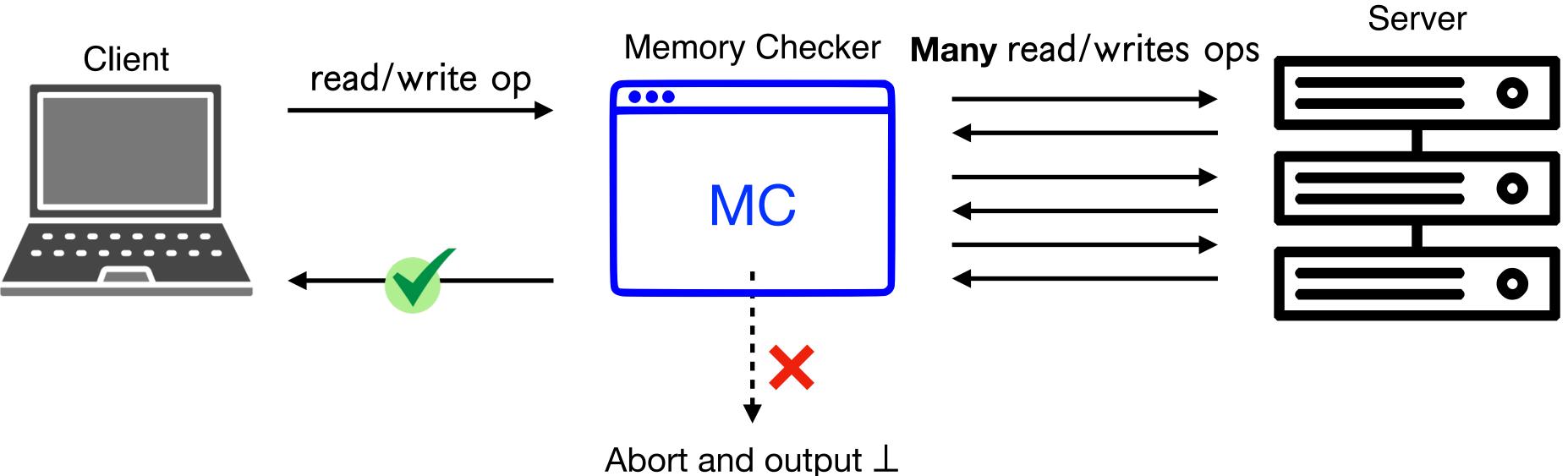

read/write op

[Blum, Evans, Gemmel, Kannan, Naor '94]

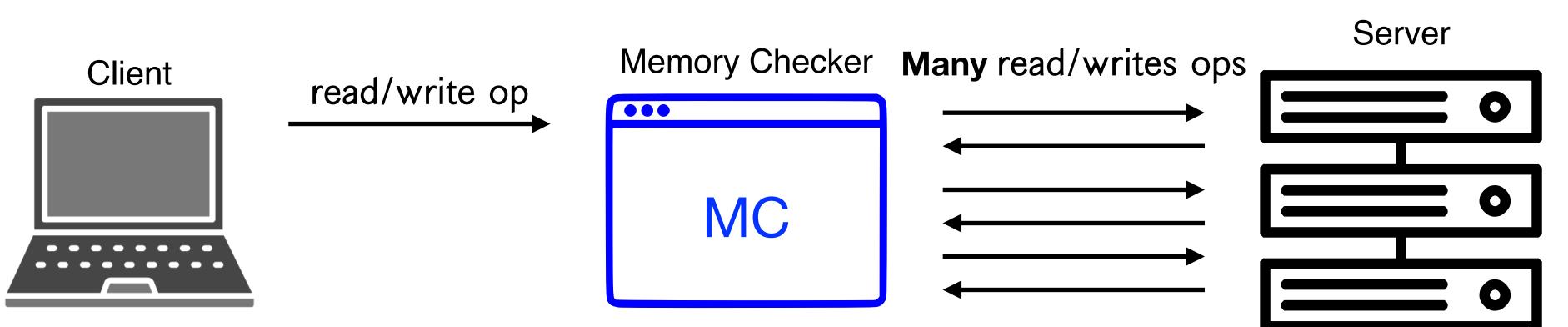

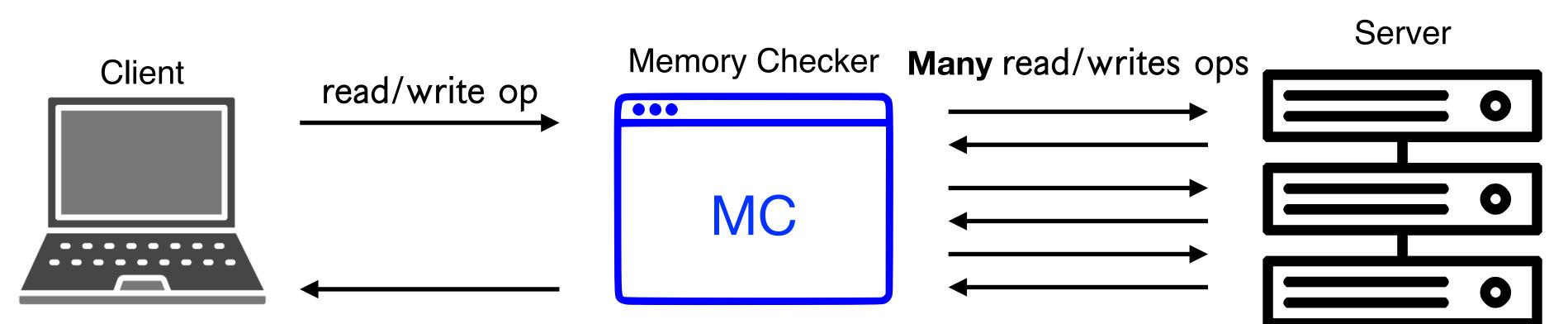

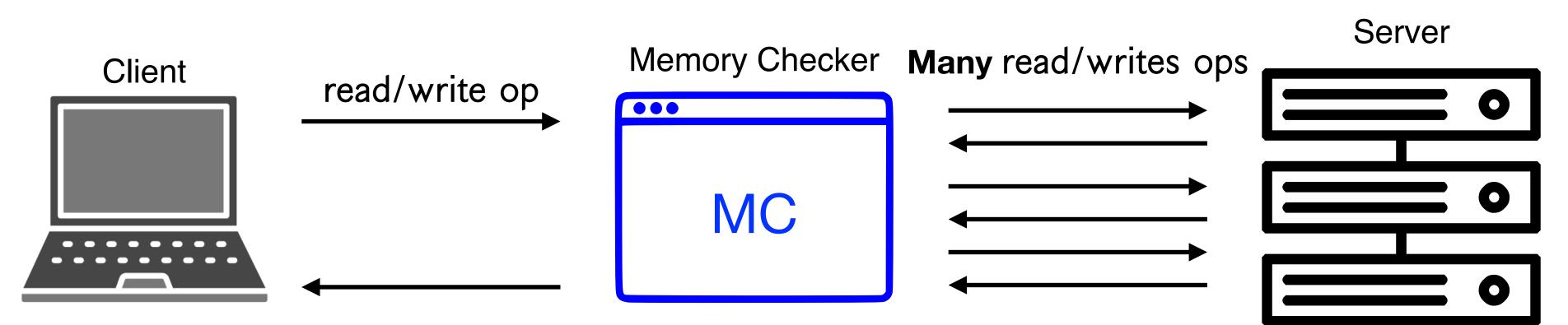

#### Memory Checking

Server

### Memory Checking

Memory Checker

MC

Server

### Memory Checking

### Memory Checking

(i.e. most recent version of address) responses.

#### **Memory Checking**

(i.e. most recent version of address) responses.

### **Memory Checking**

Abort and output  $\perp$

(i.e. most recent version of address) responses.

### **Memory Checking**

Abort and output  $\perp$

- (i.e. most recent version of address) responses.

- Completeness: If the server behaves honestly, MC doesn't abort.

### **Memory Checking**

• Examples

- **Examples**

- Shared database across many clients

- **Examples**

- Shared database across many clients

- CPUs with shared memory

- **Examples**

- Shared database across many clients

- CPUs with shared memory

- Distributed computing

- **Examples**

- Shared database across many clients

- CPUs with shared memory

- Distributed computing

- Integrity verification is very useful here too!

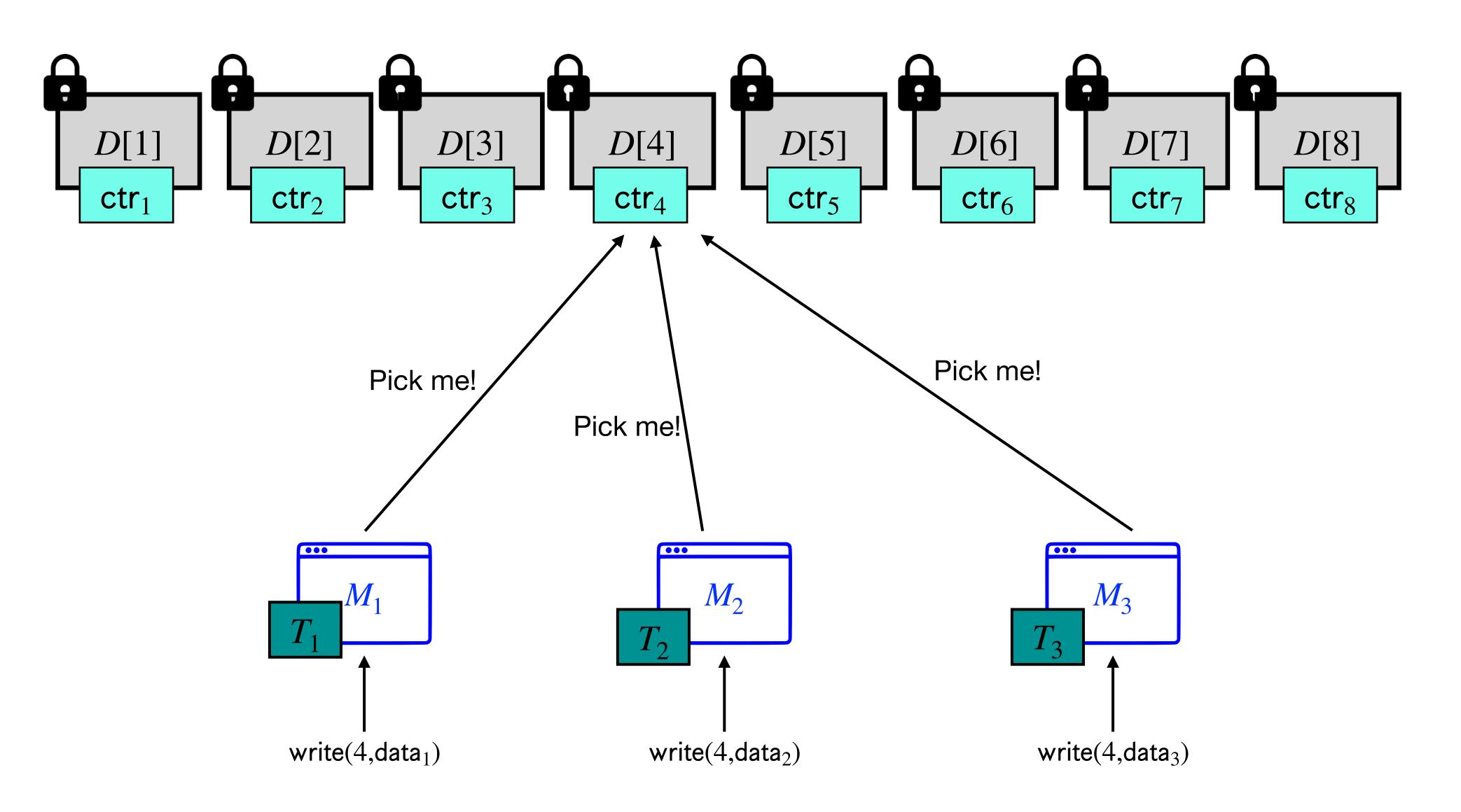

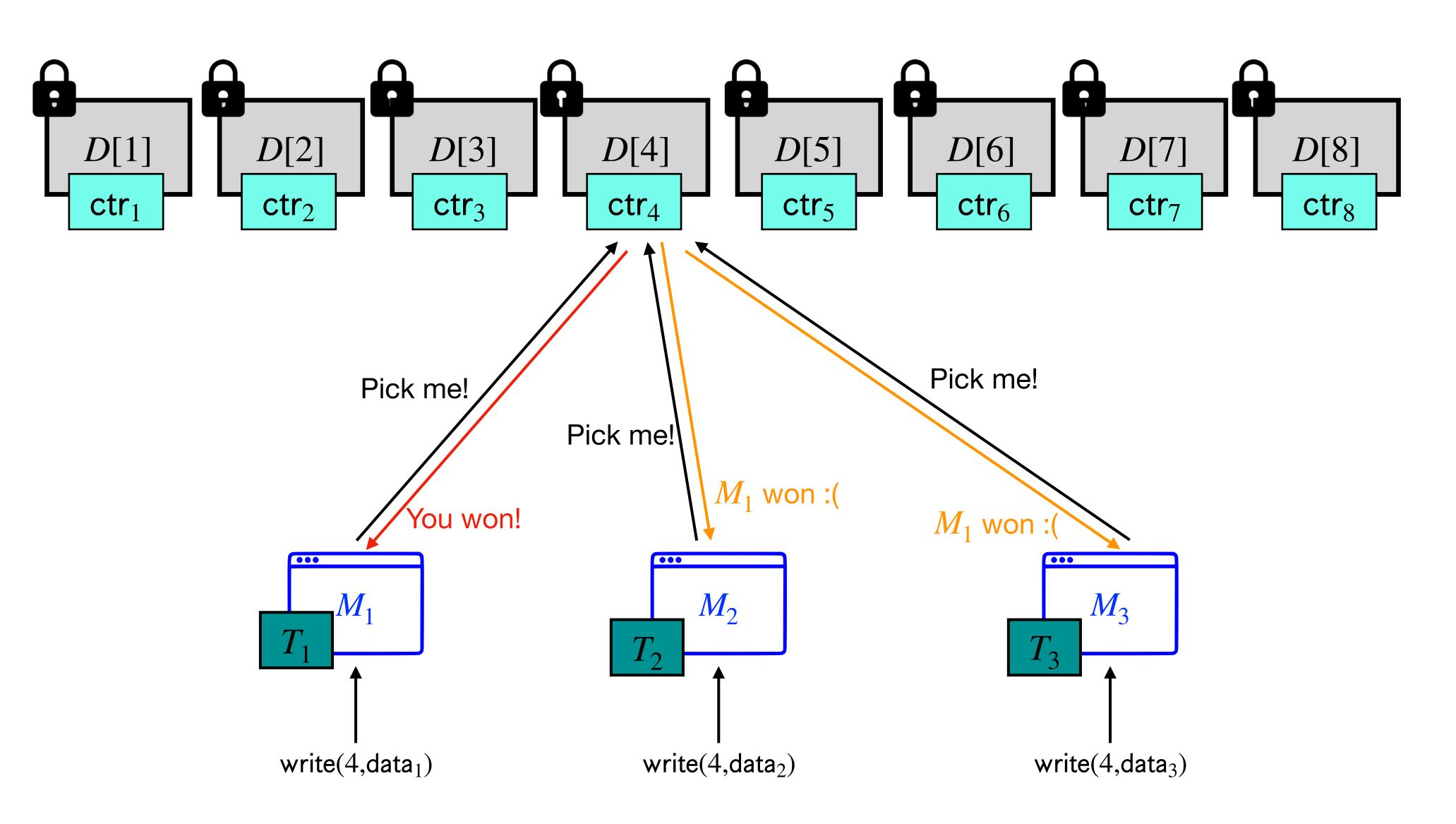

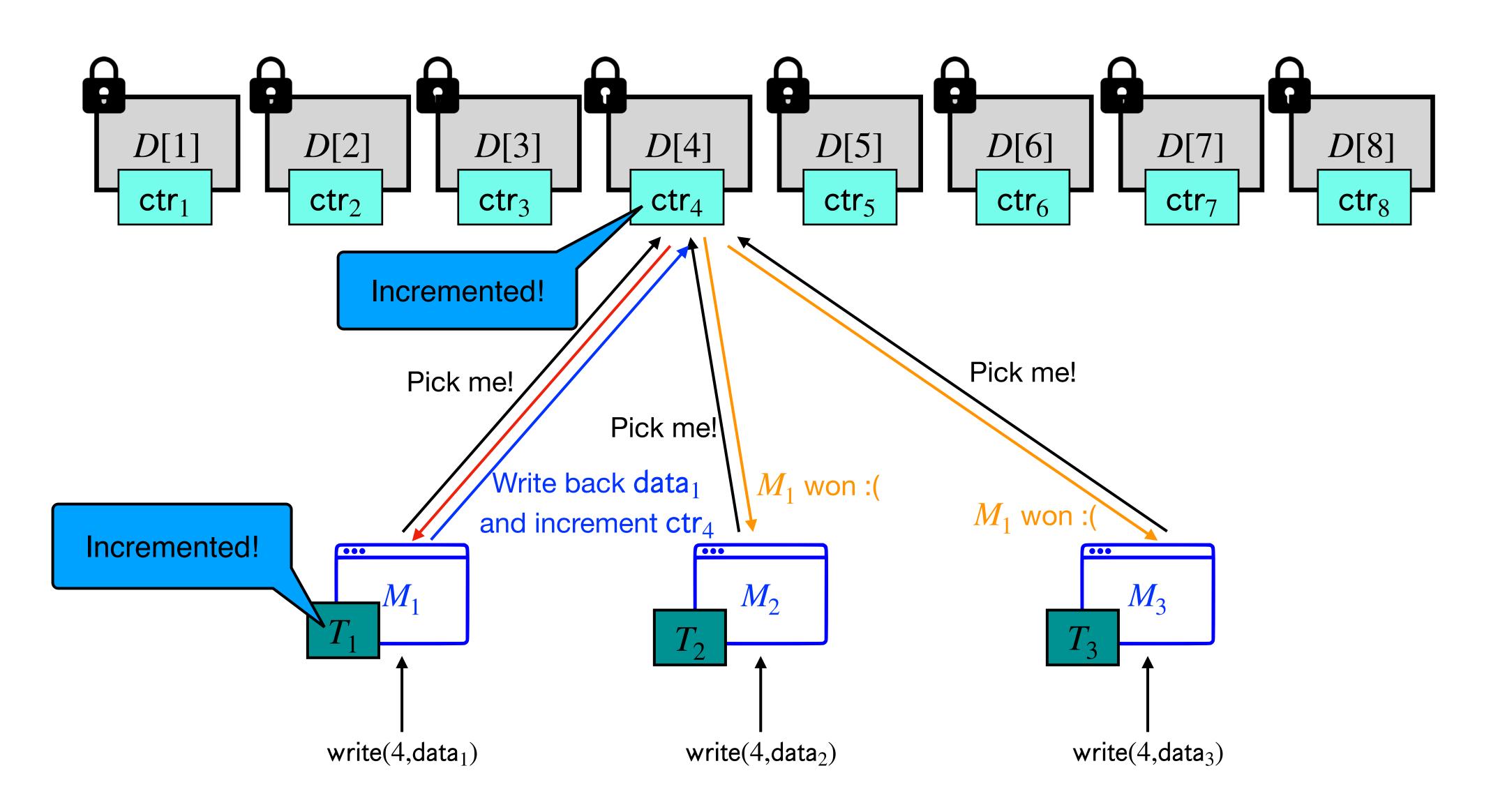

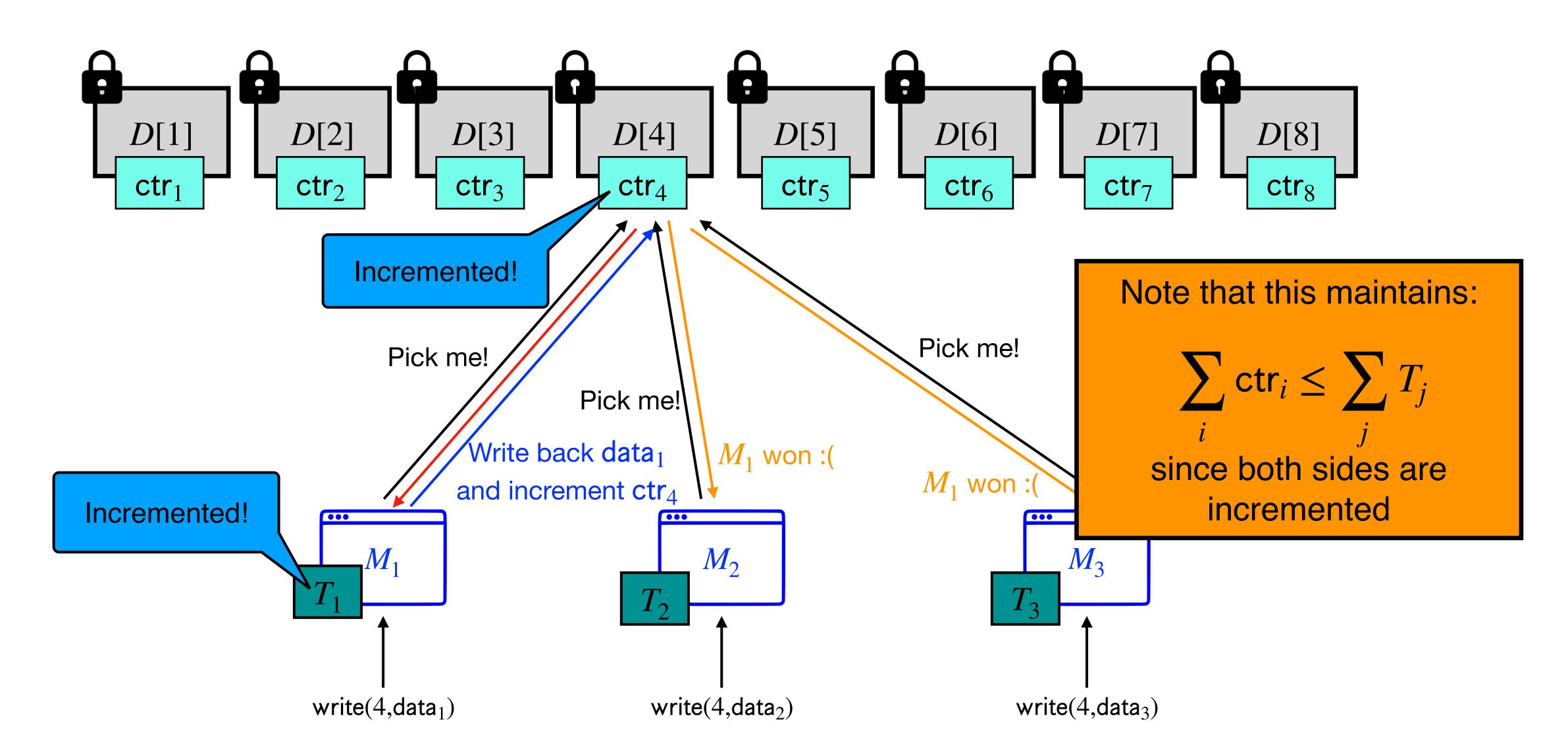

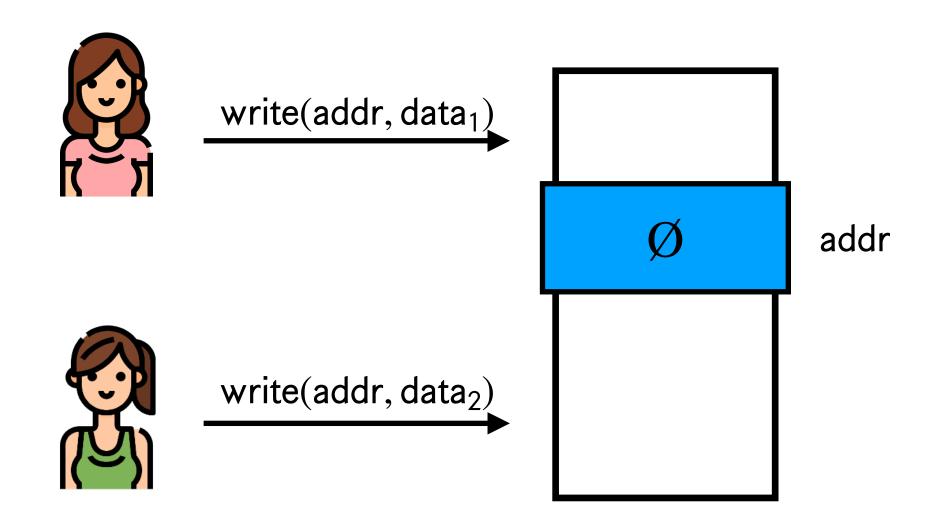

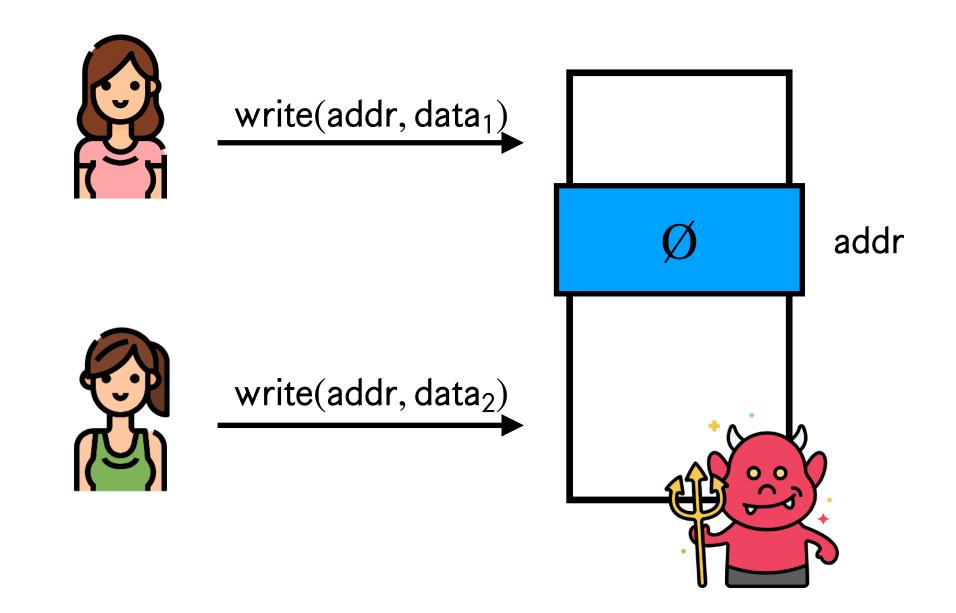

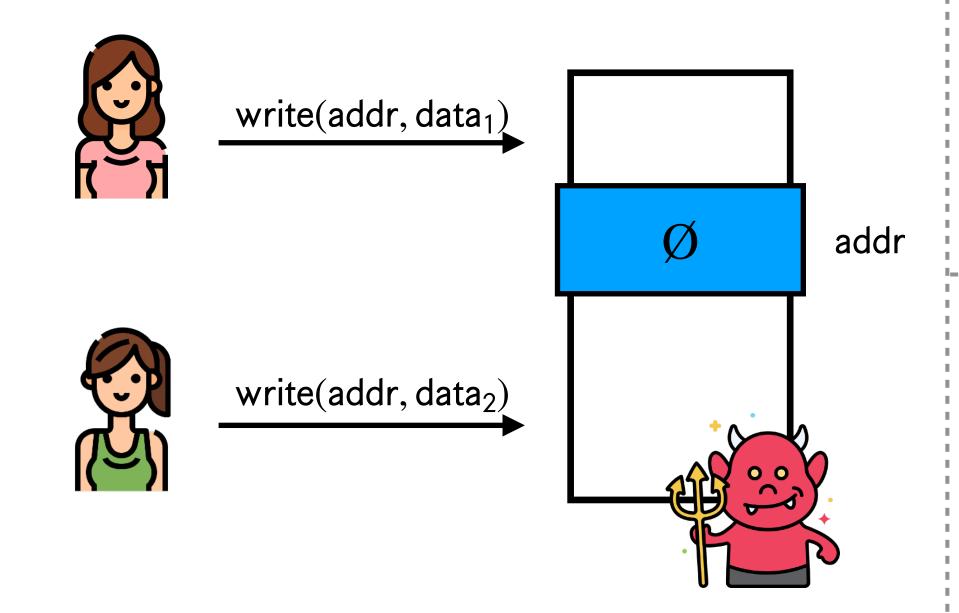

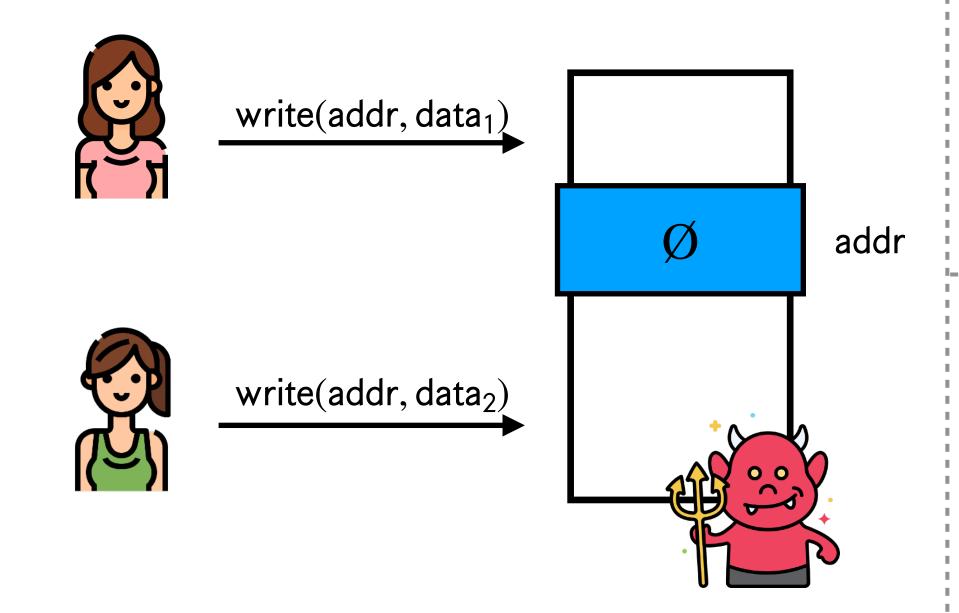

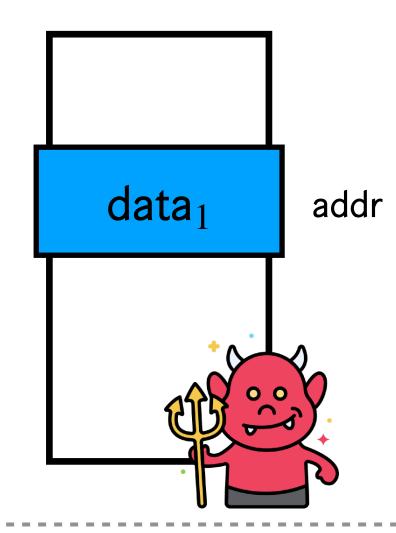

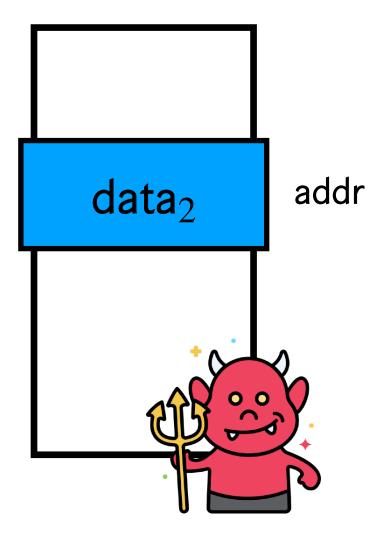

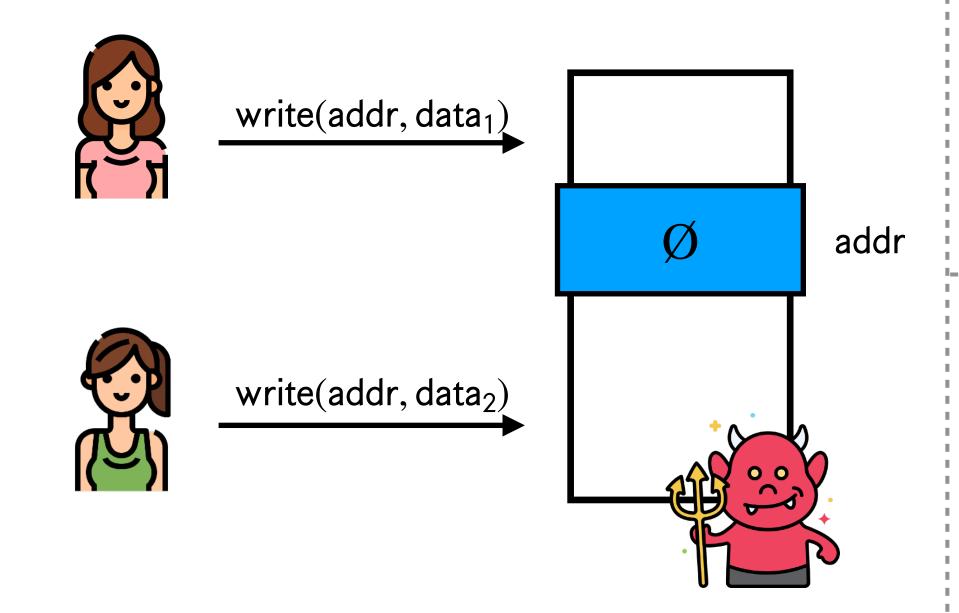

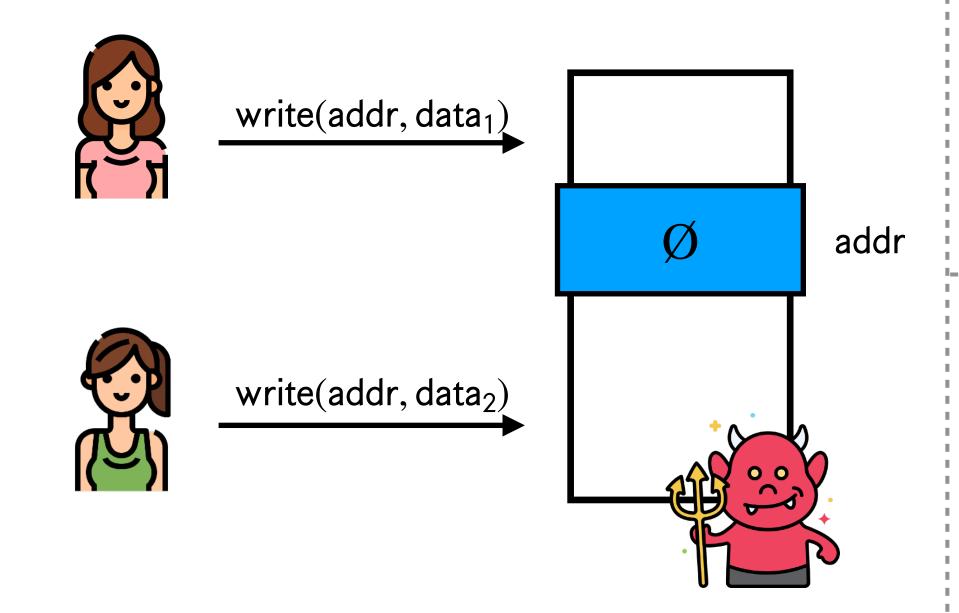

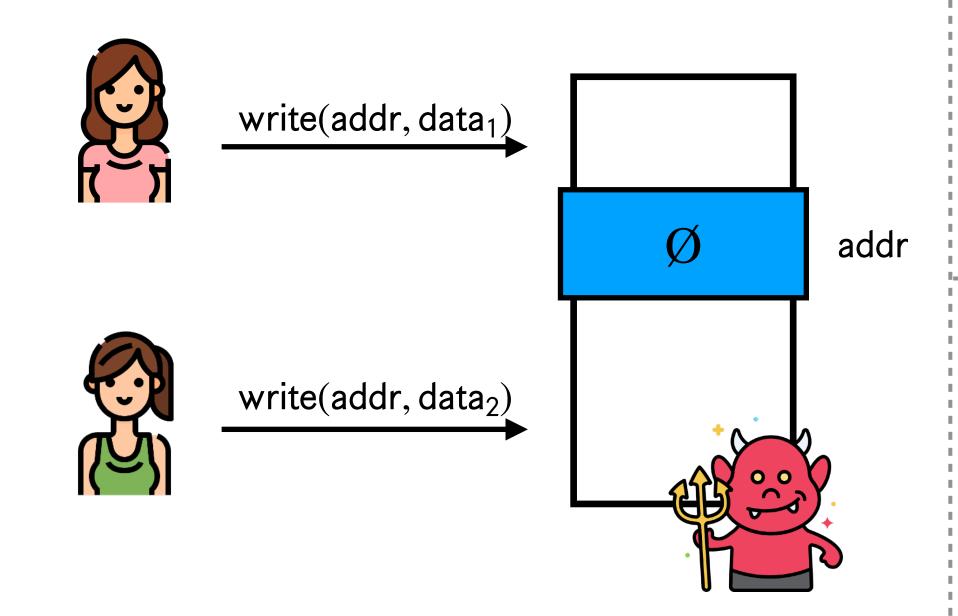

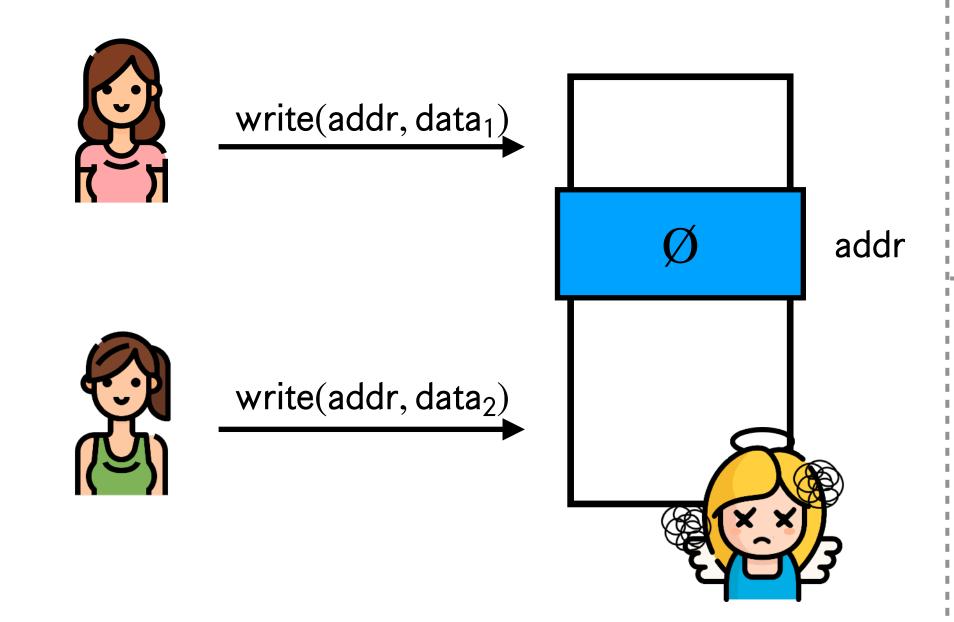

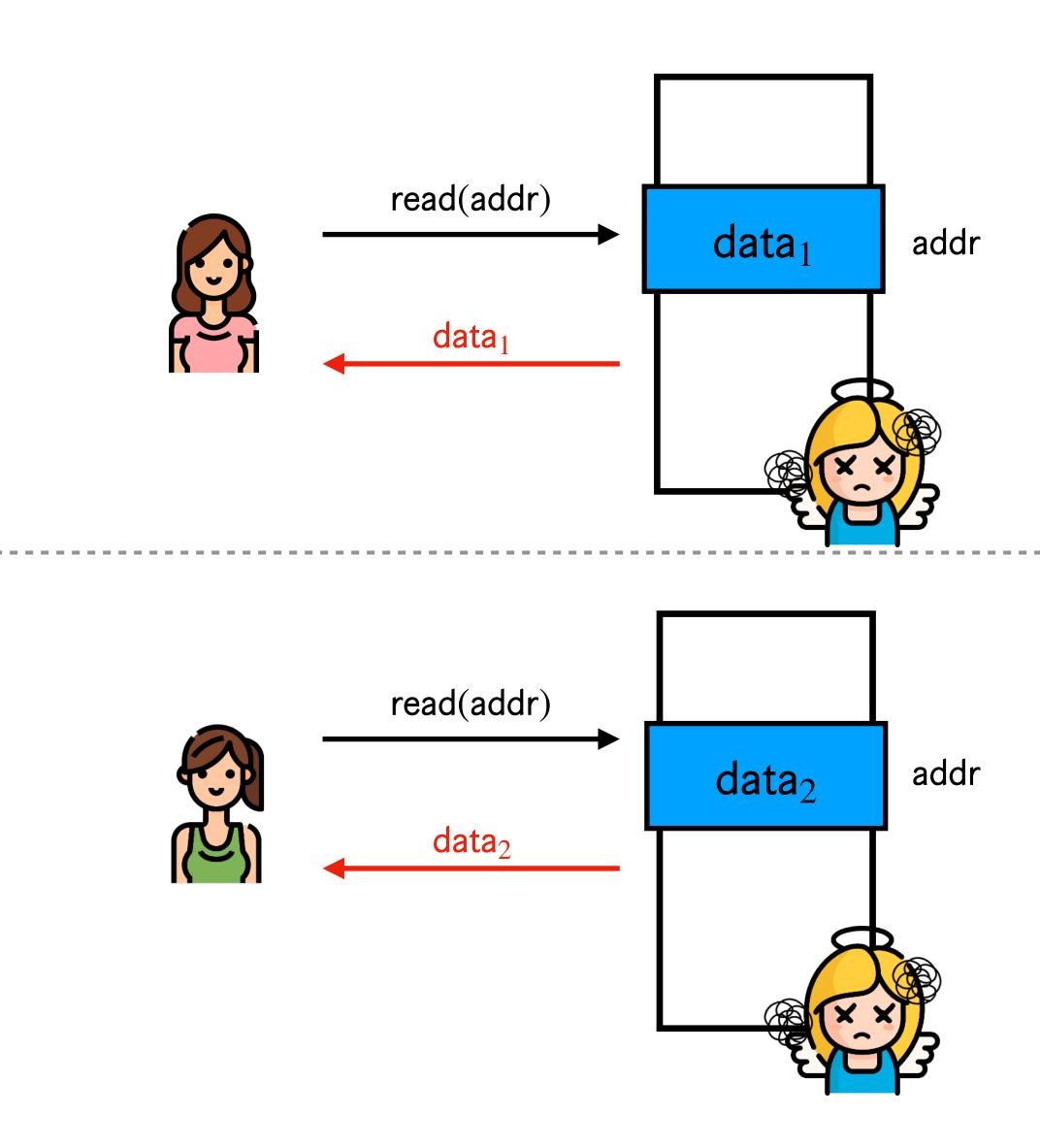

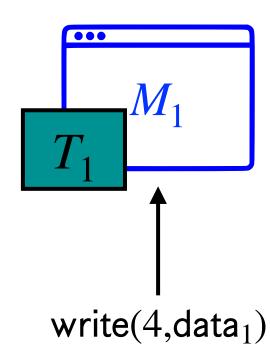

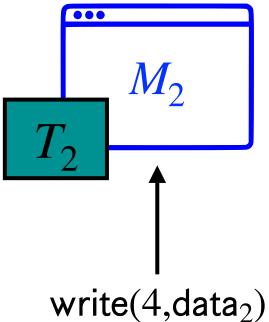

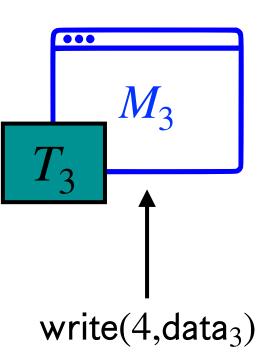

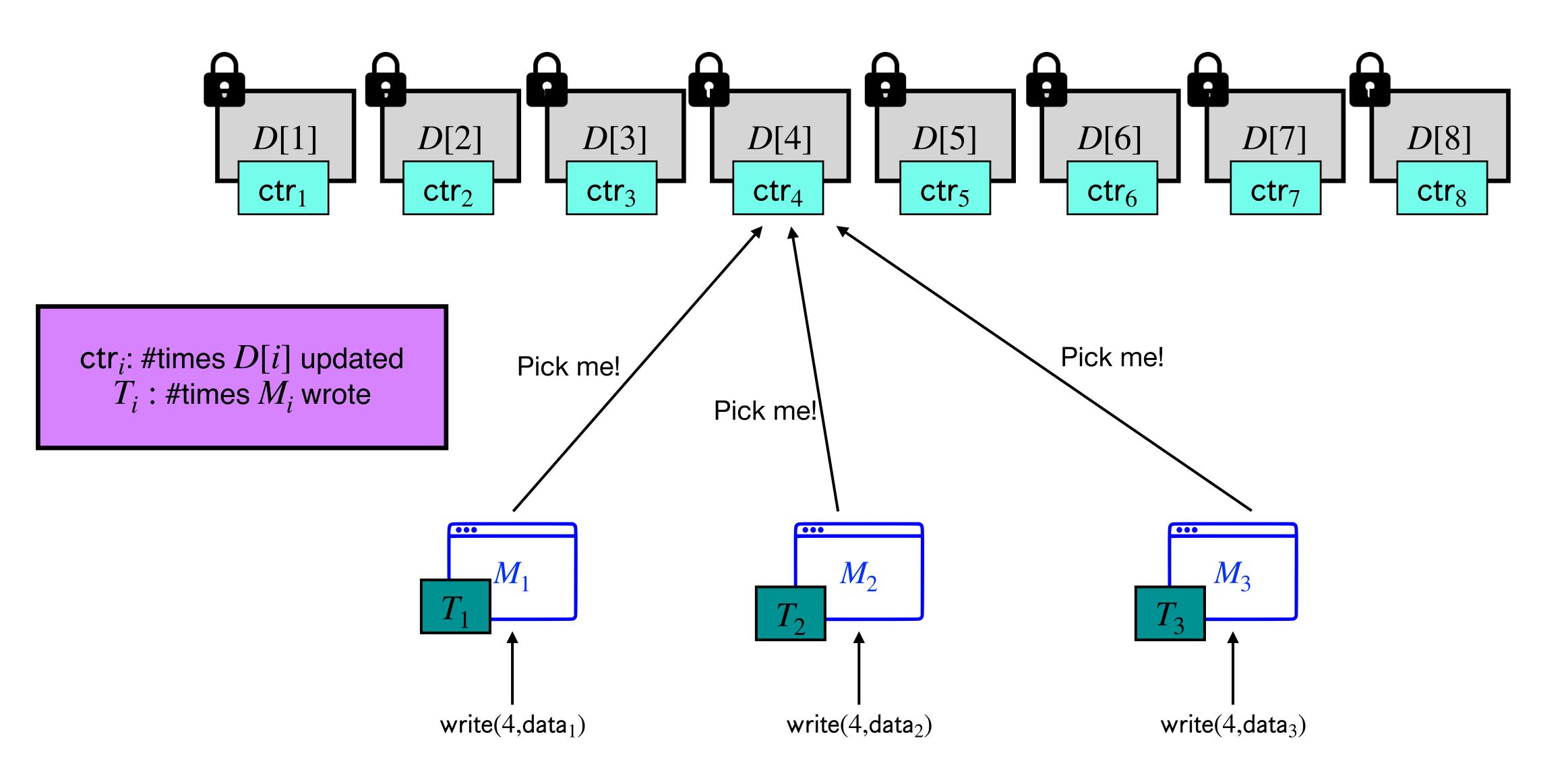

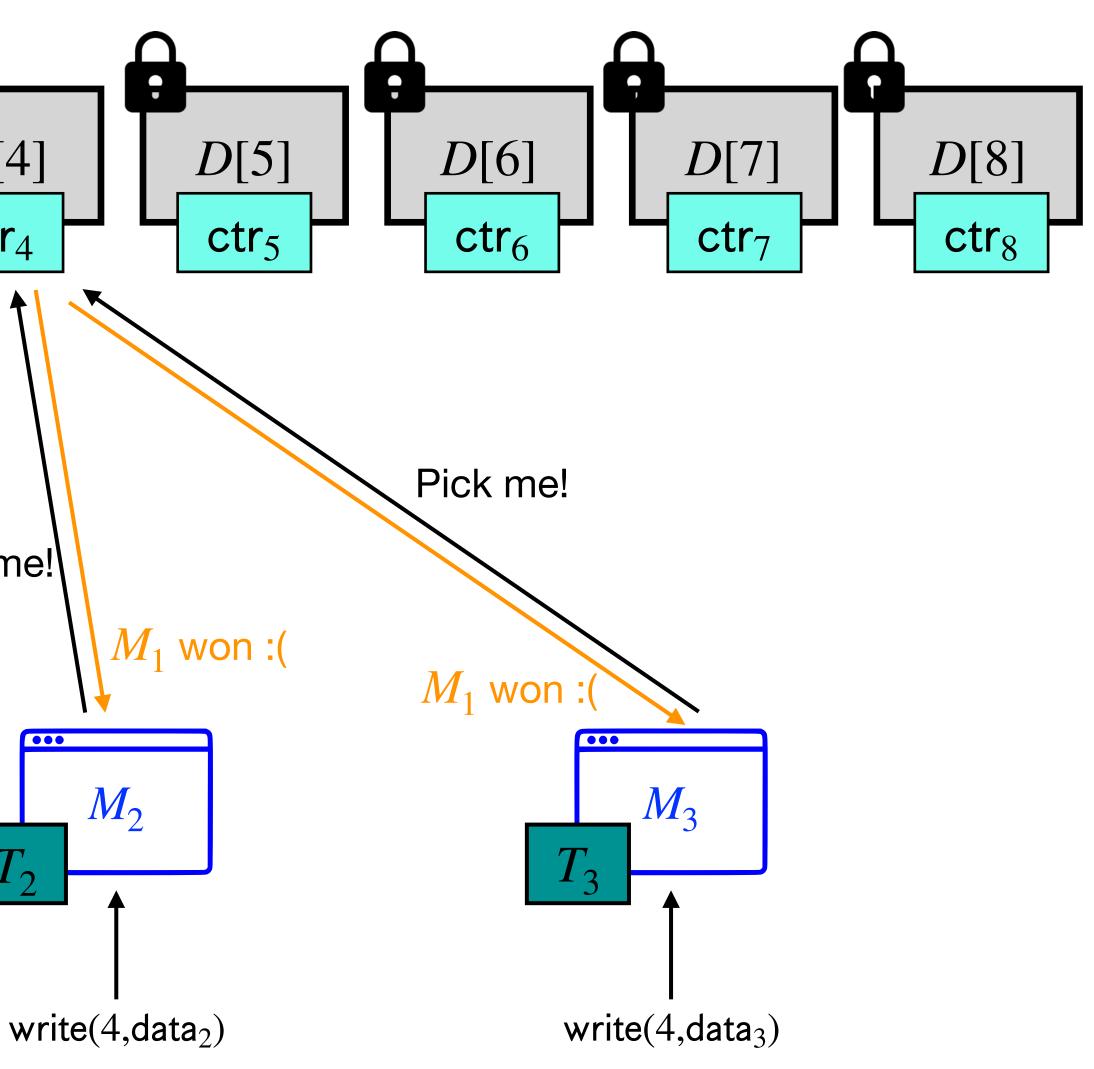

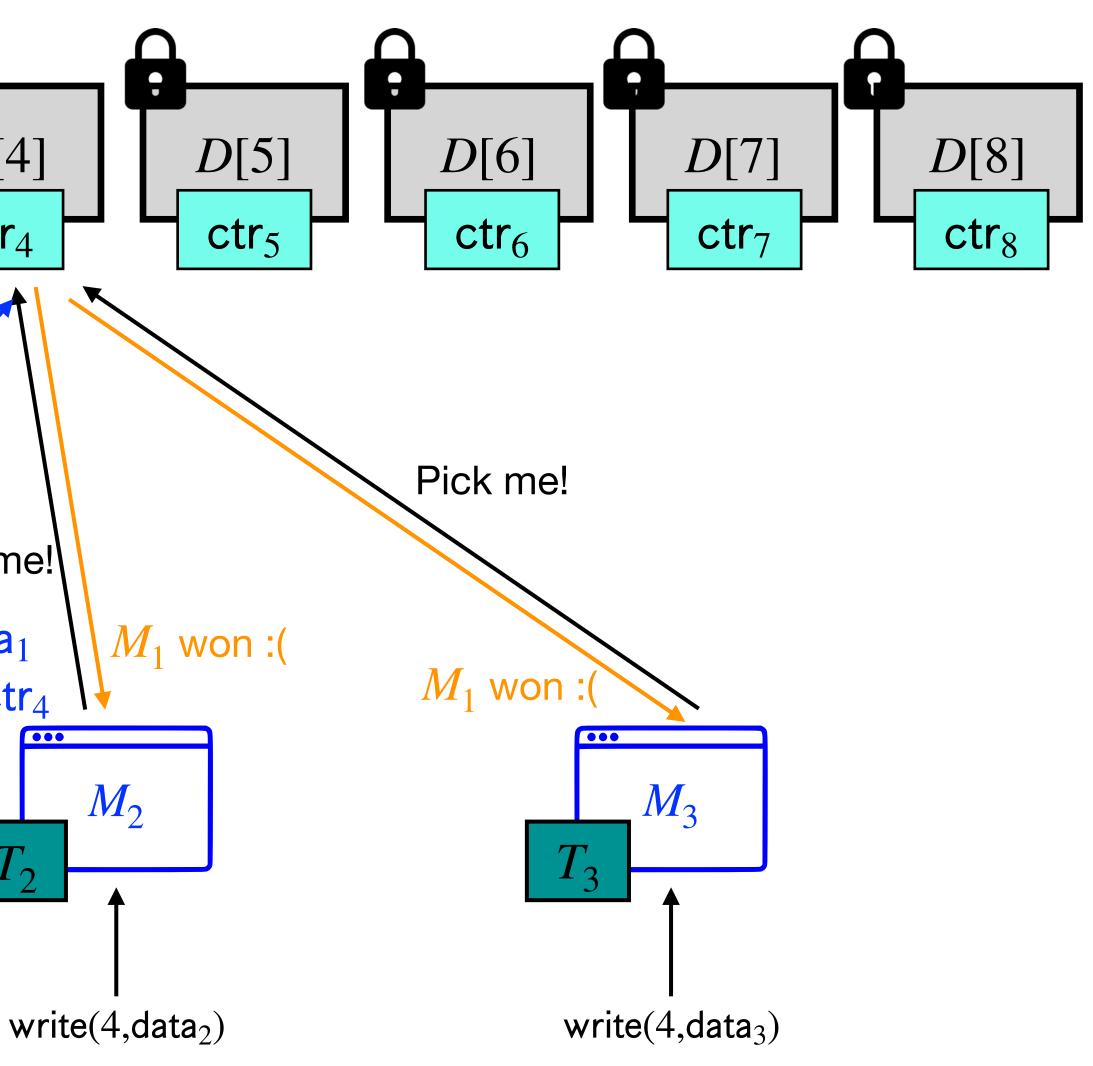

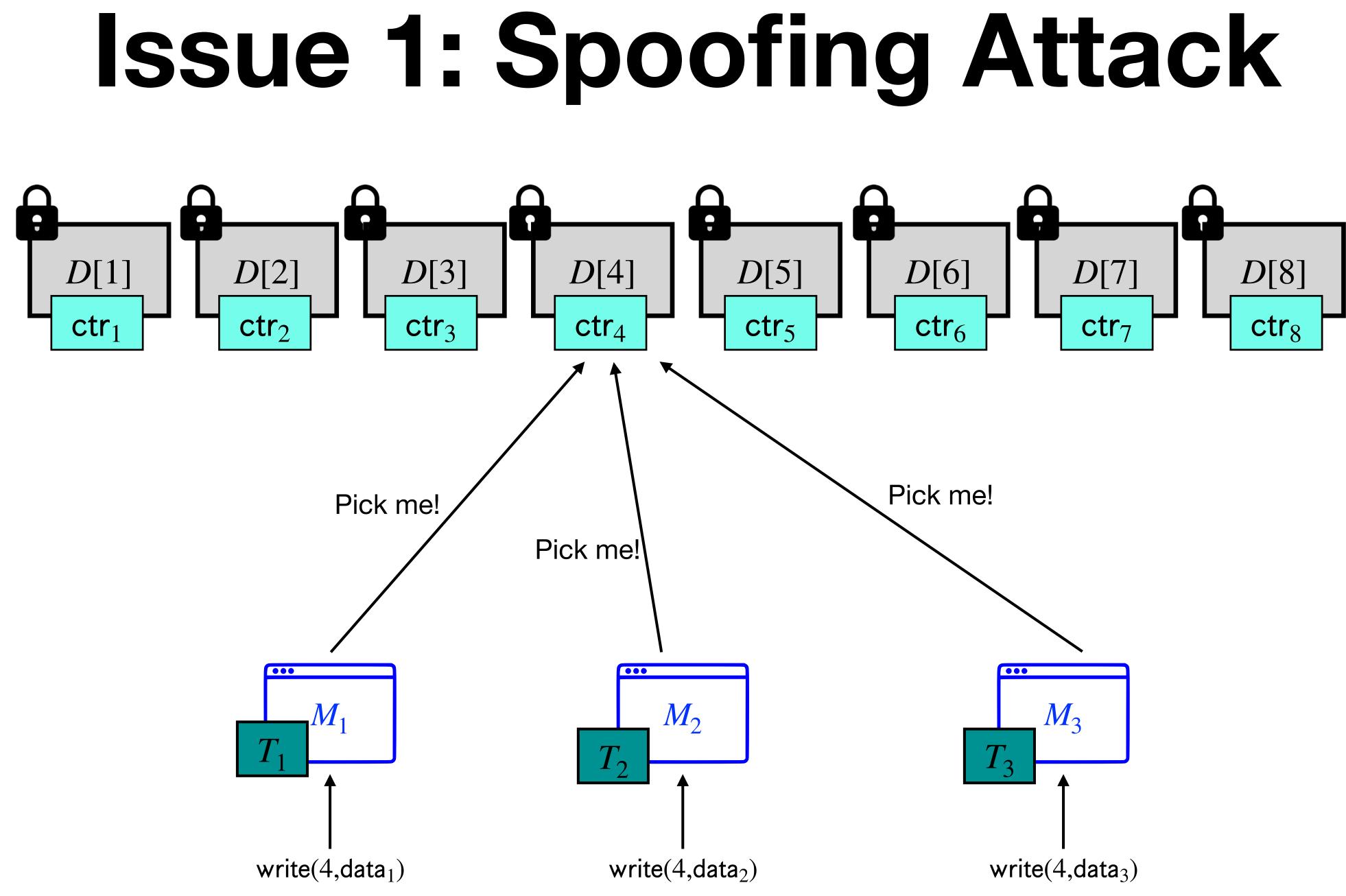

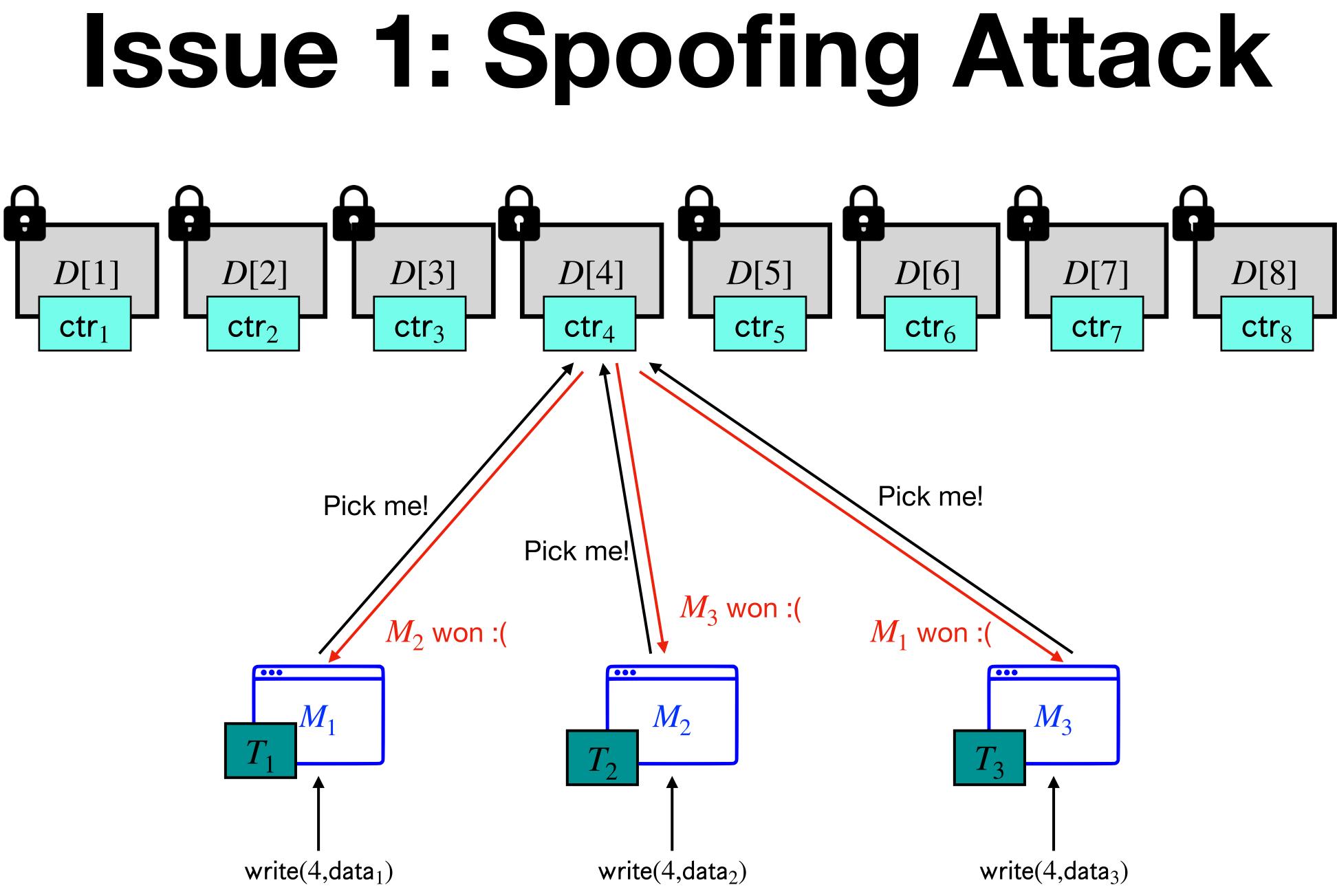

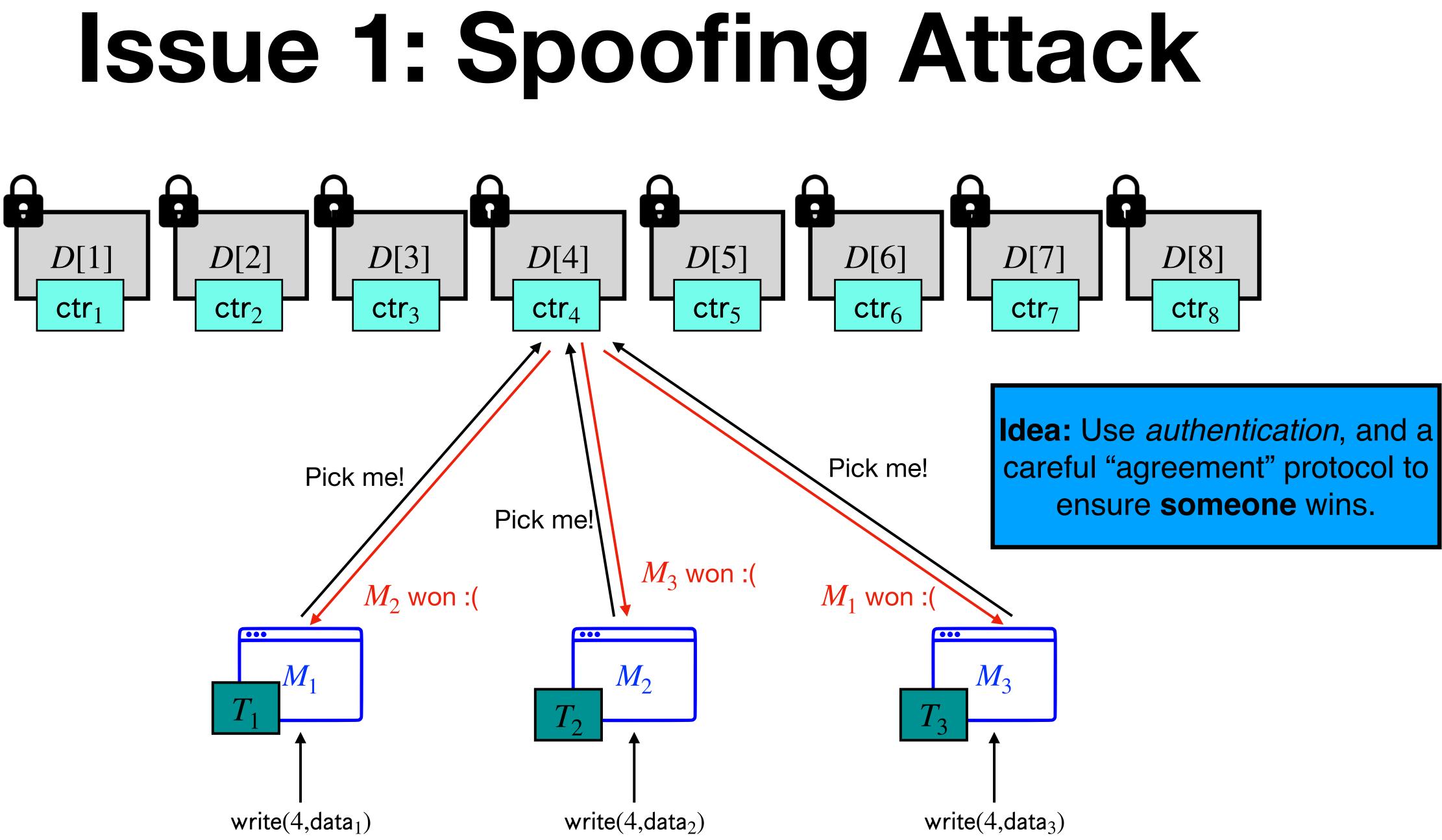

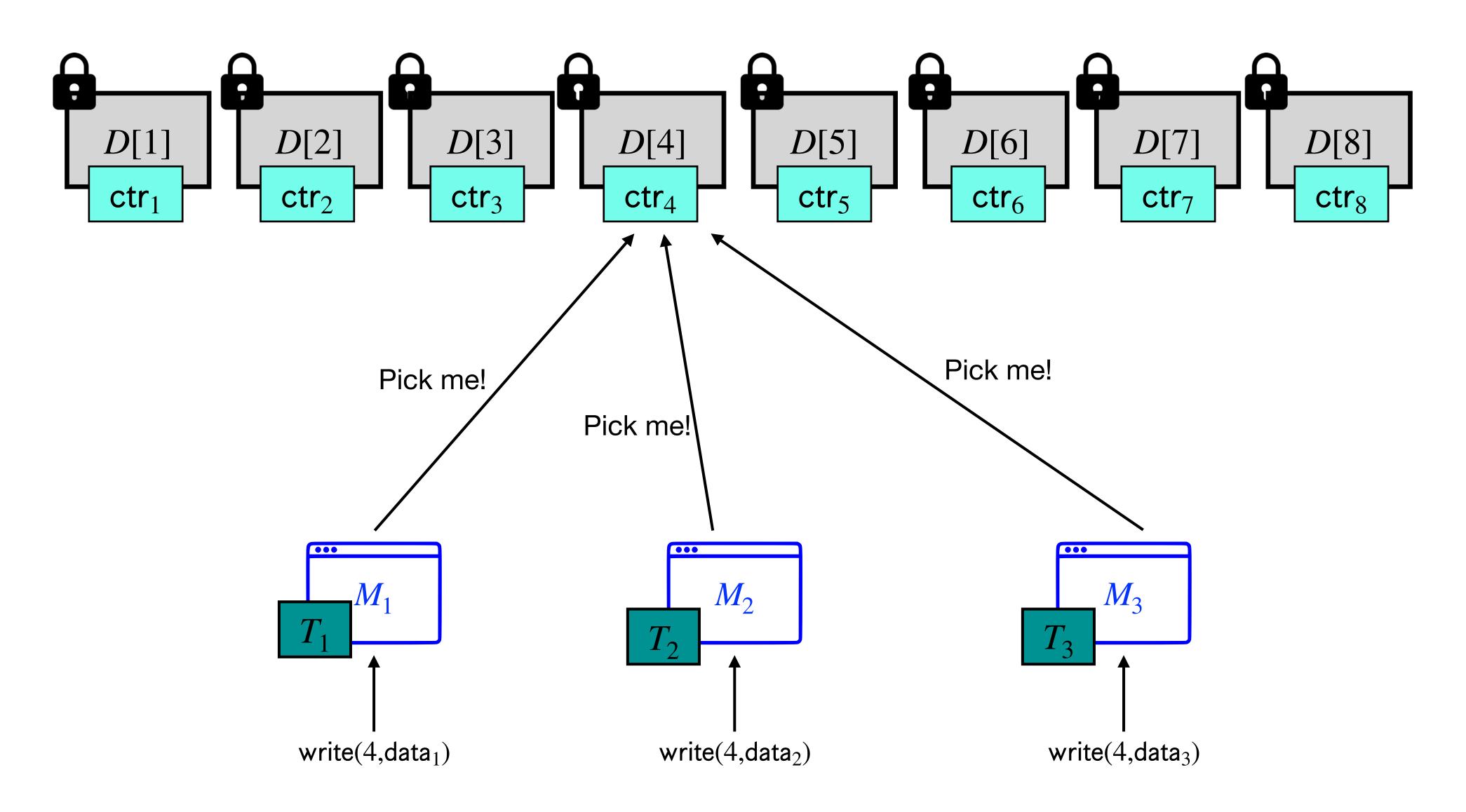

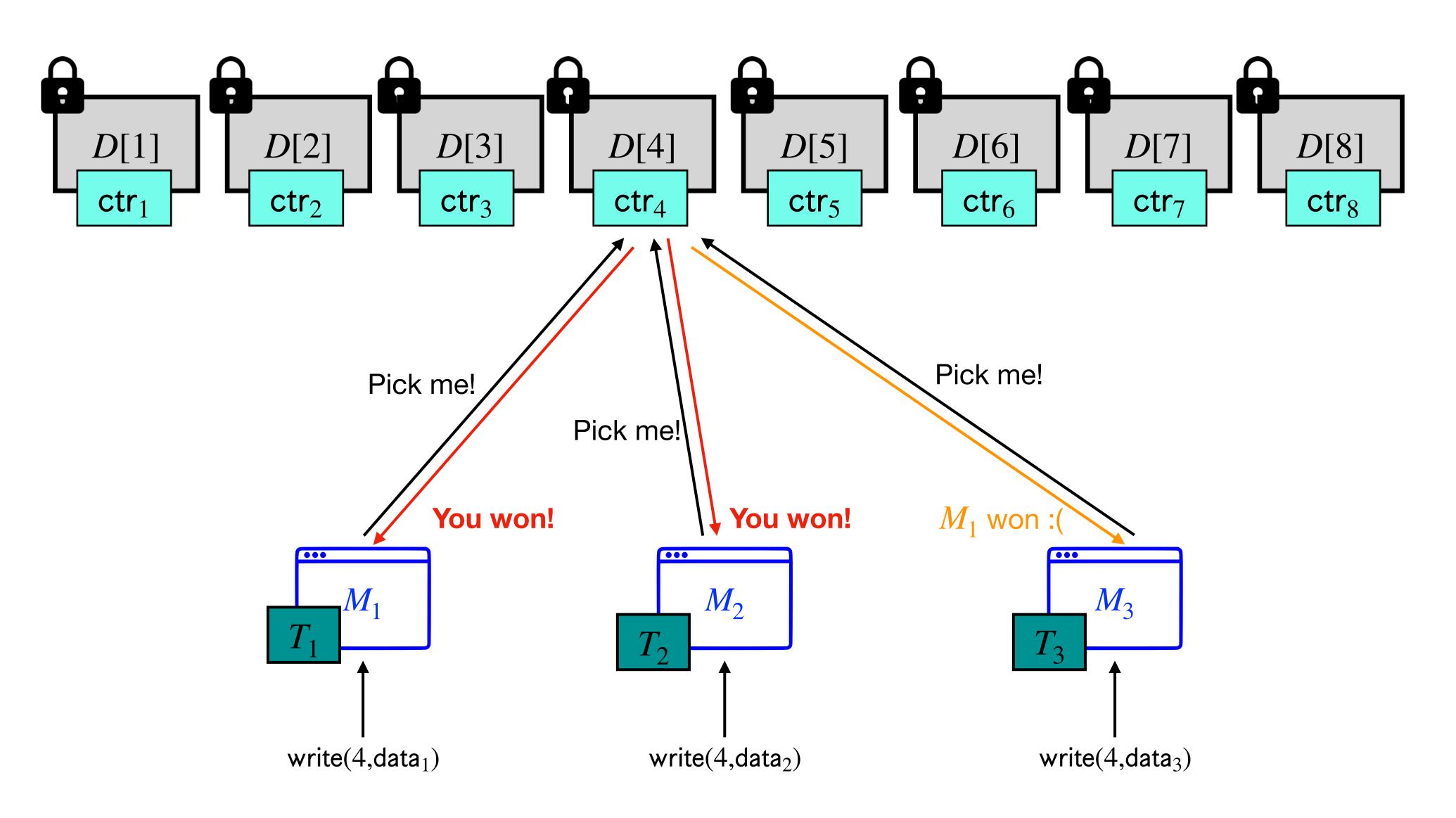

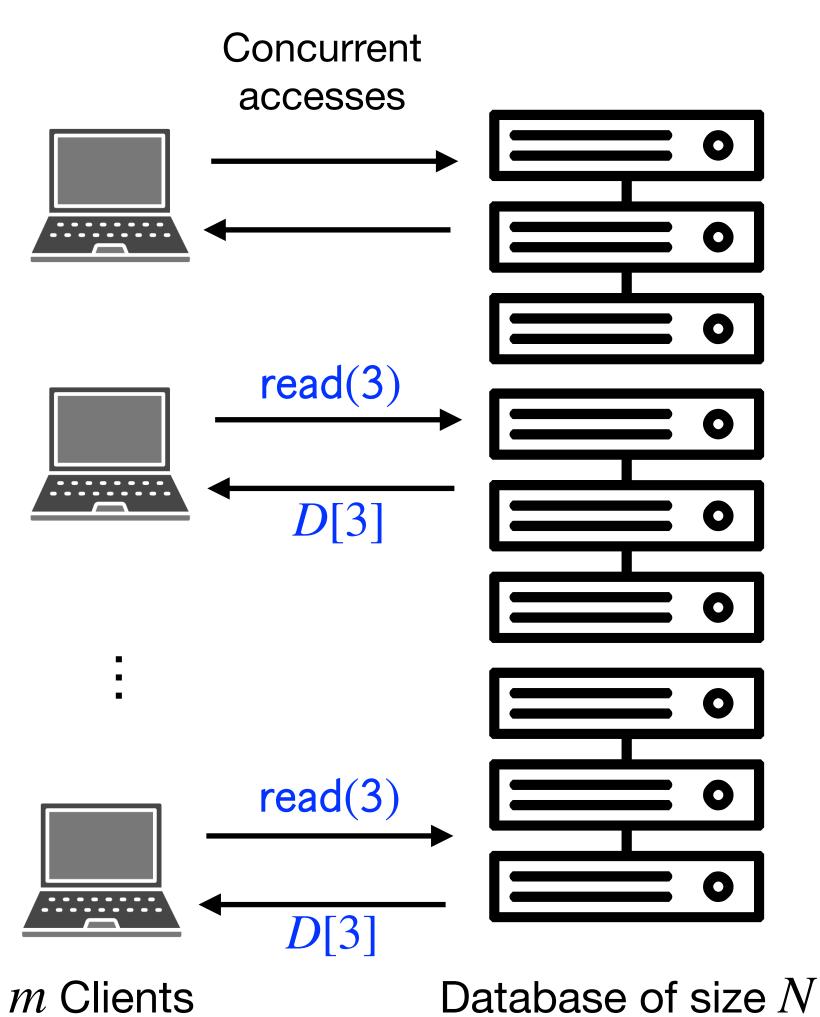

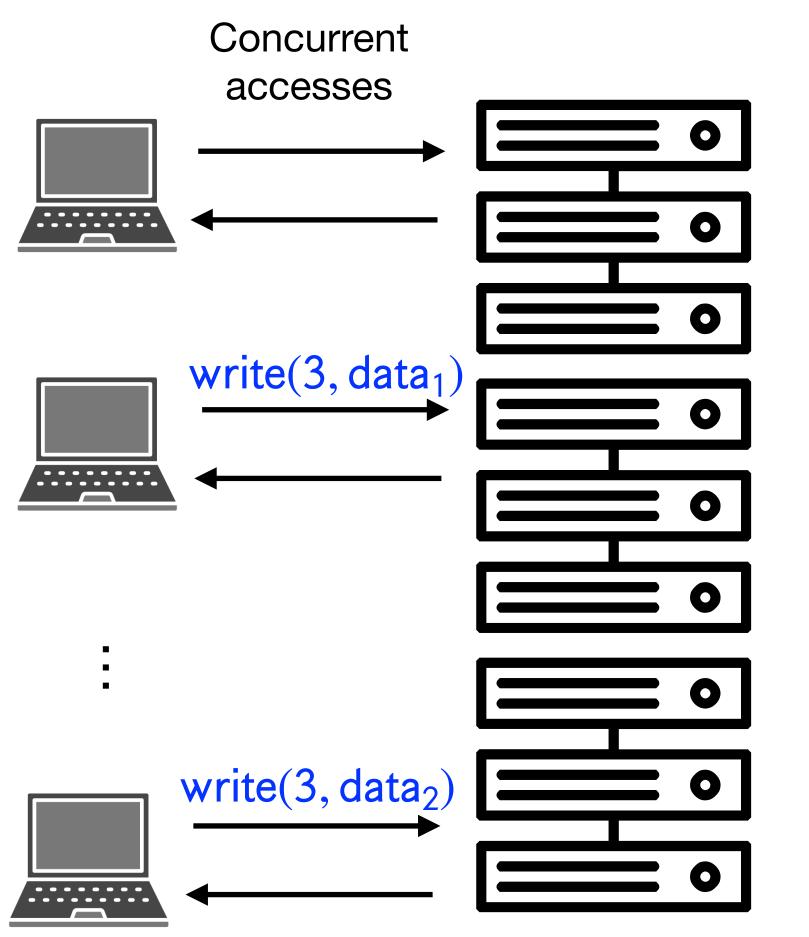

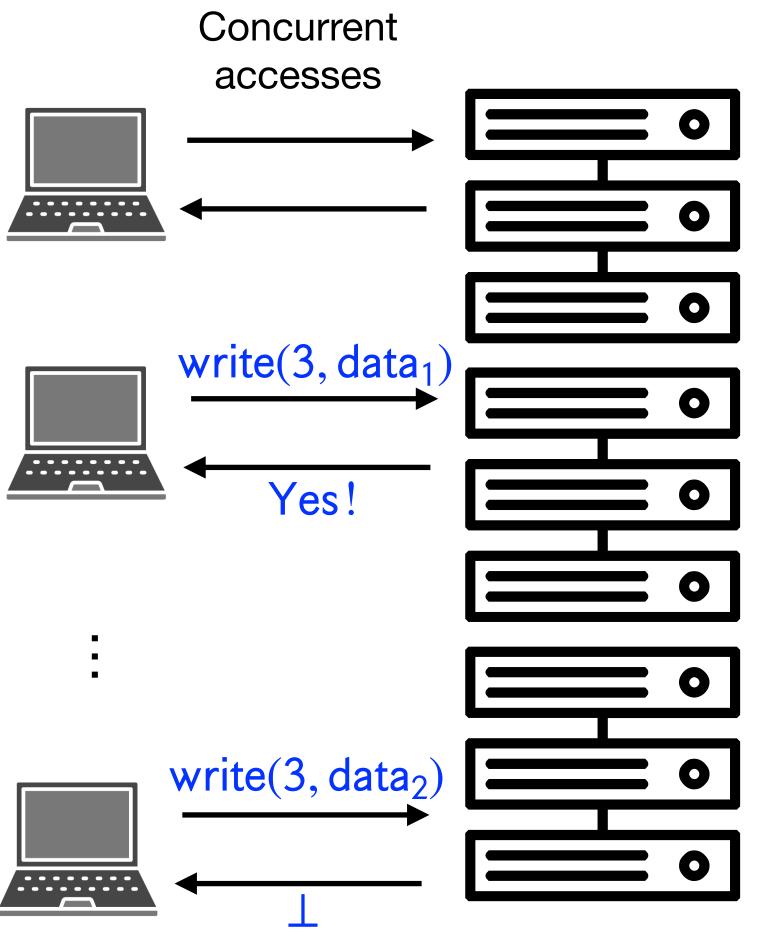

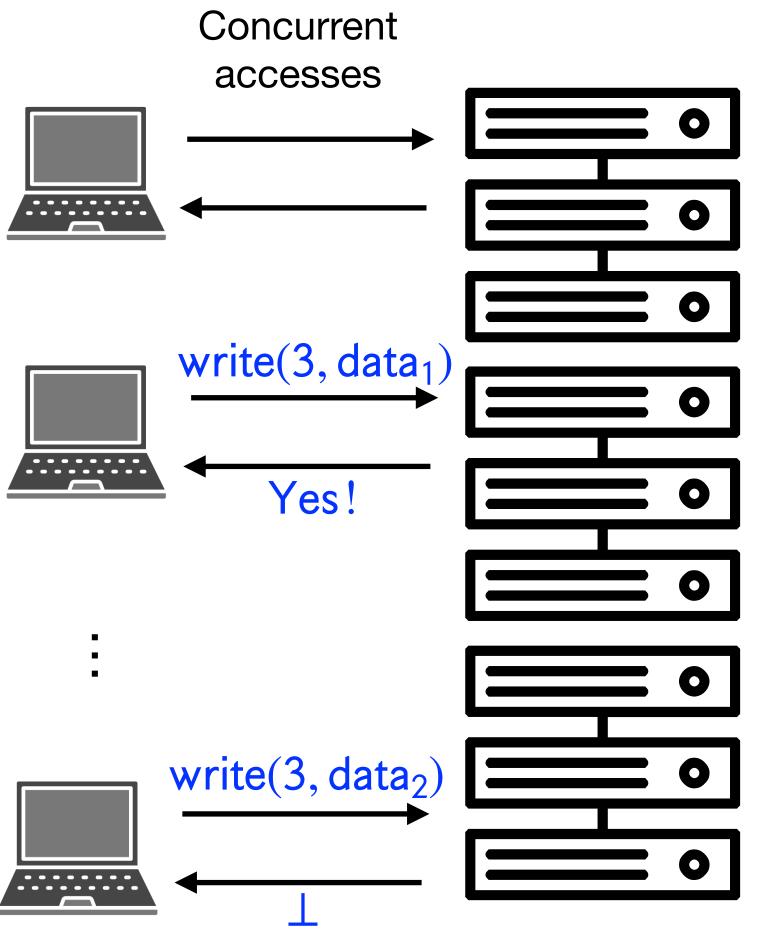

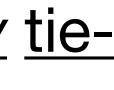

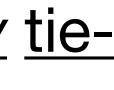

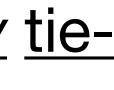

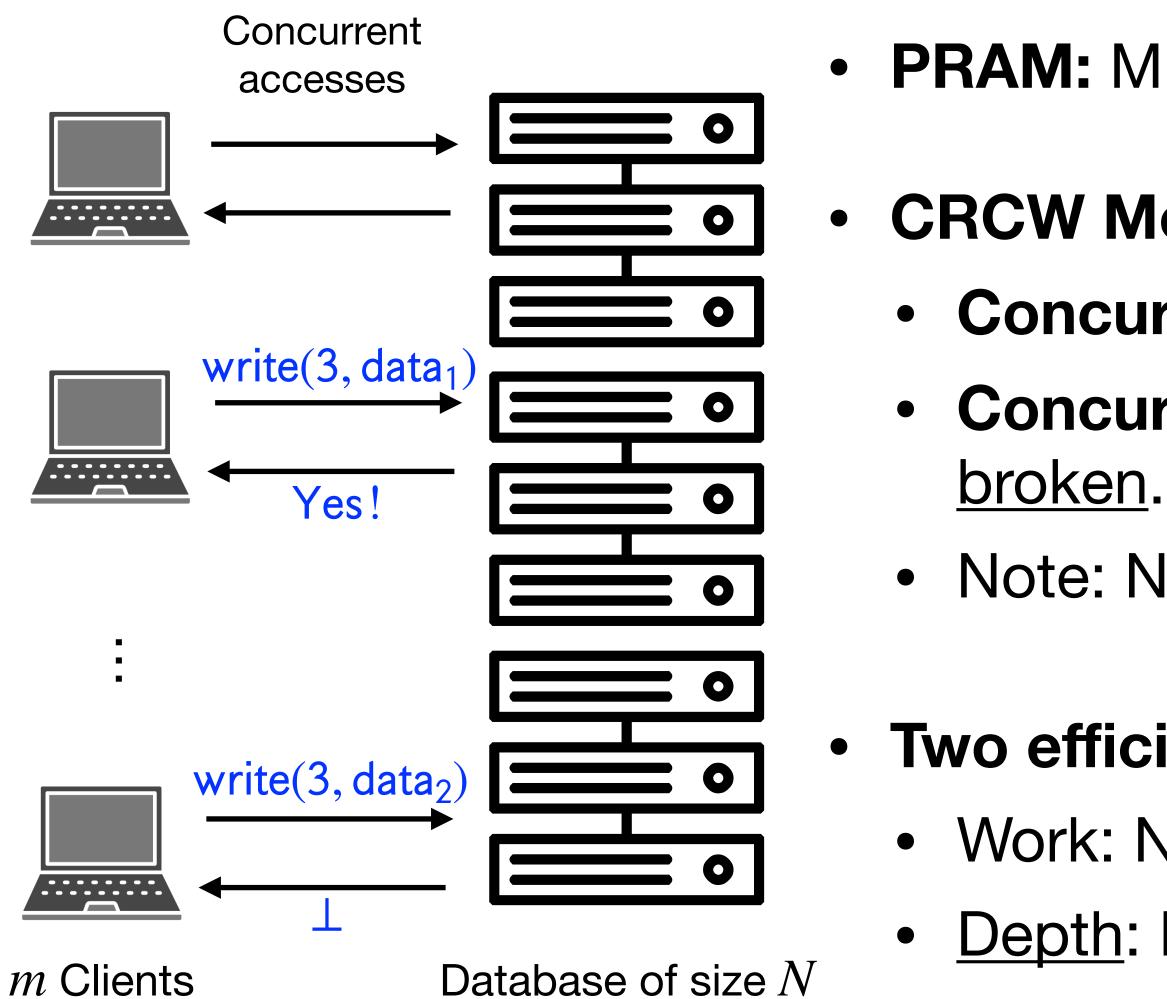

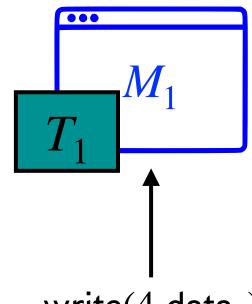

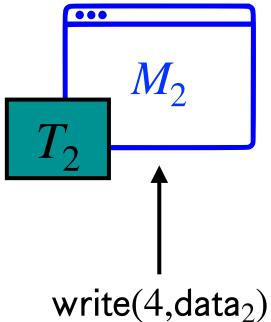

Consider two concurrent writes:

Consider two concurrent writes:

Consider two concurrent writes:

This "branching" might happen even when the server makes an "**honest** mistake"!!

Consider two concurrent writes:

This "branching" might happen even when the server makes an "**honest** mistake"!!

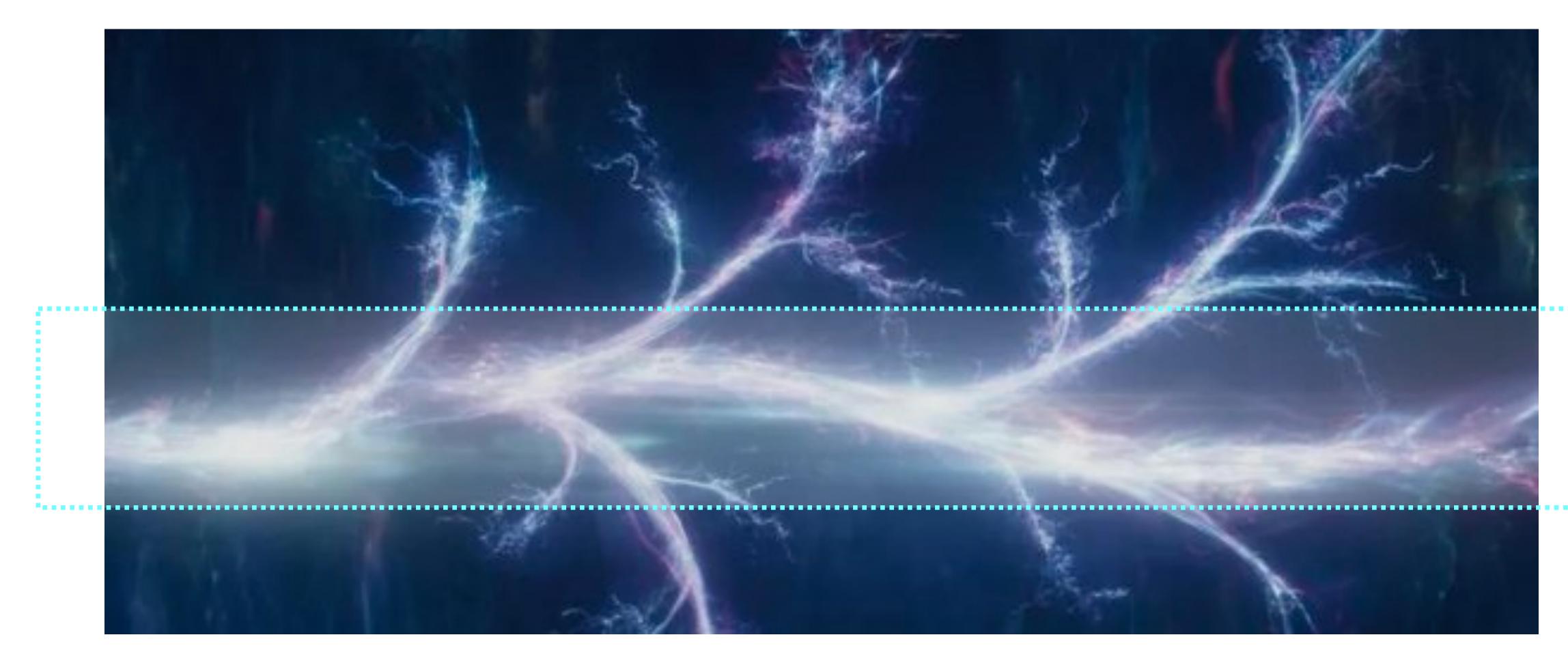

## **Branching Timelines**

From Marvel TV Series: Loki

## **Branching Timelines**

From Marvel TV Series: Loki

## **Branching Timelines**

From Marvel TV Series: Loki

We need to maintain a single consistent version of the database (or *sacred timeline*) across all the clients!

# Our Definition

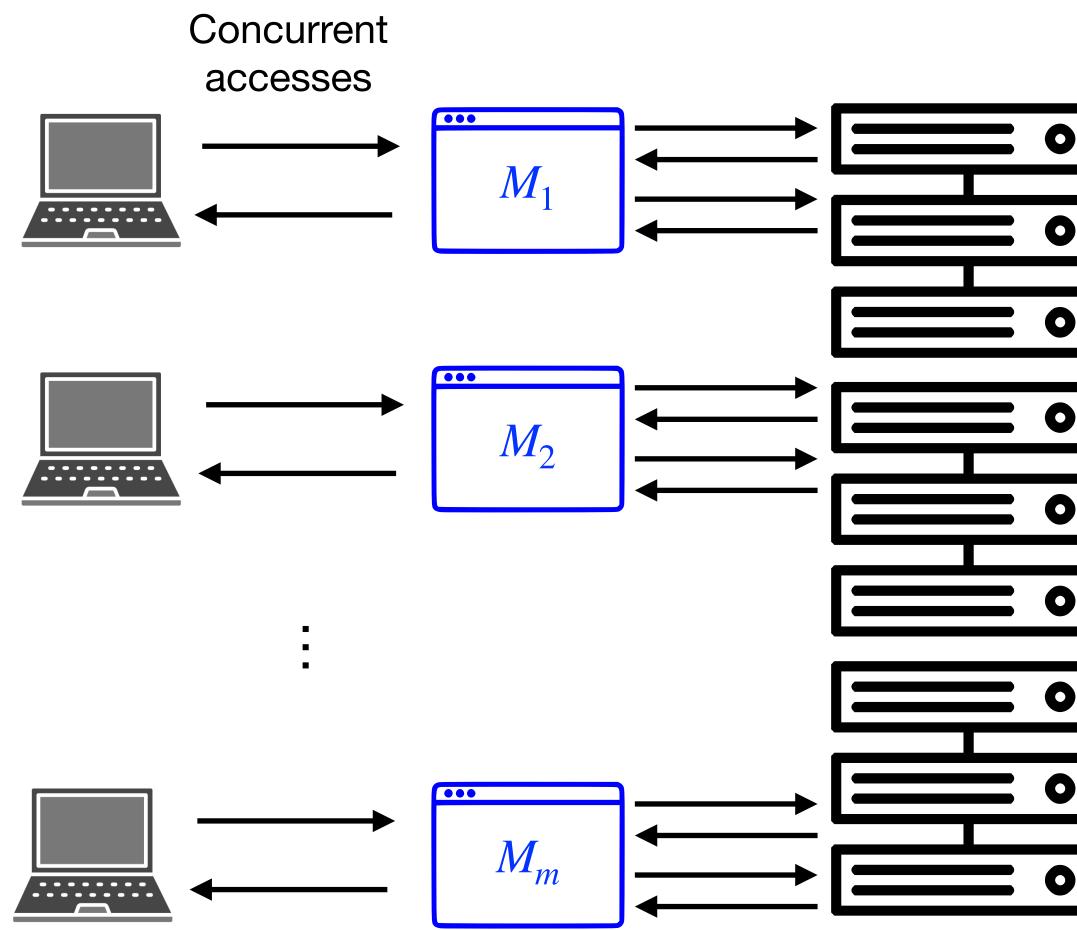

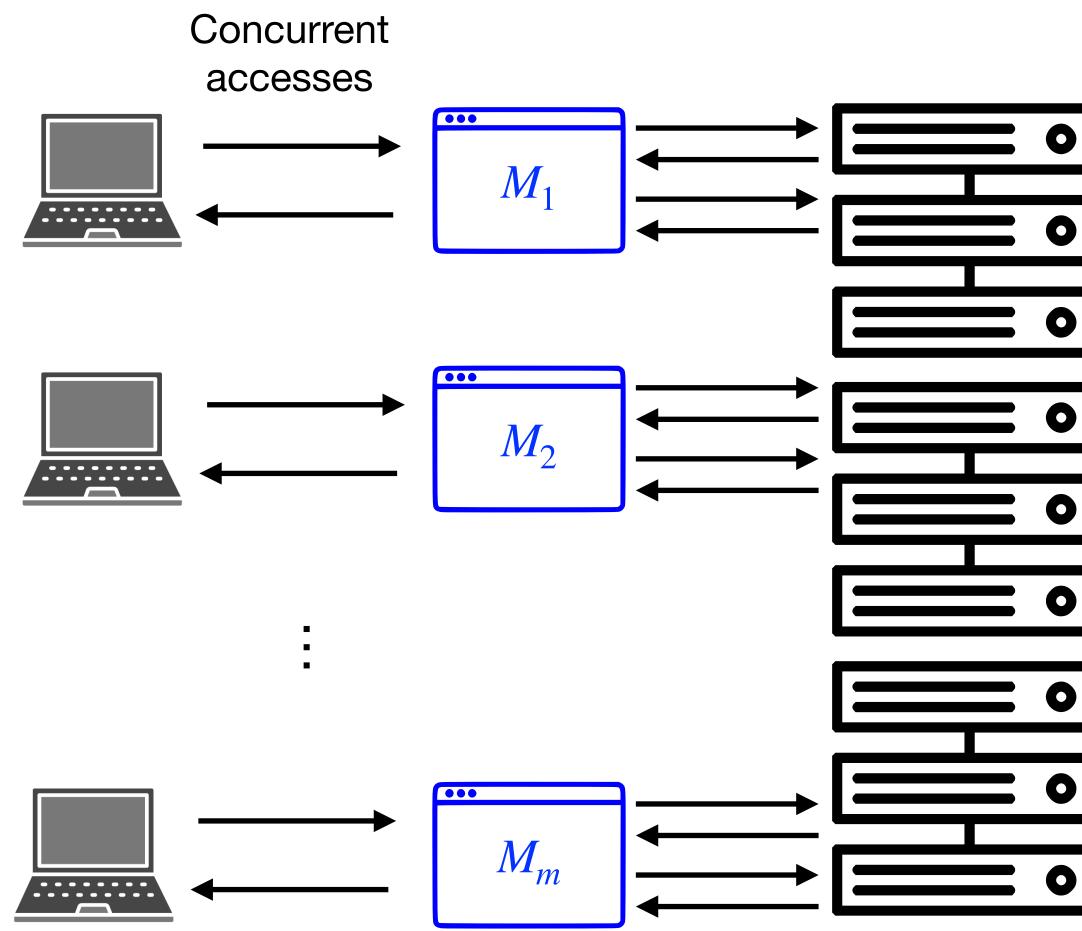

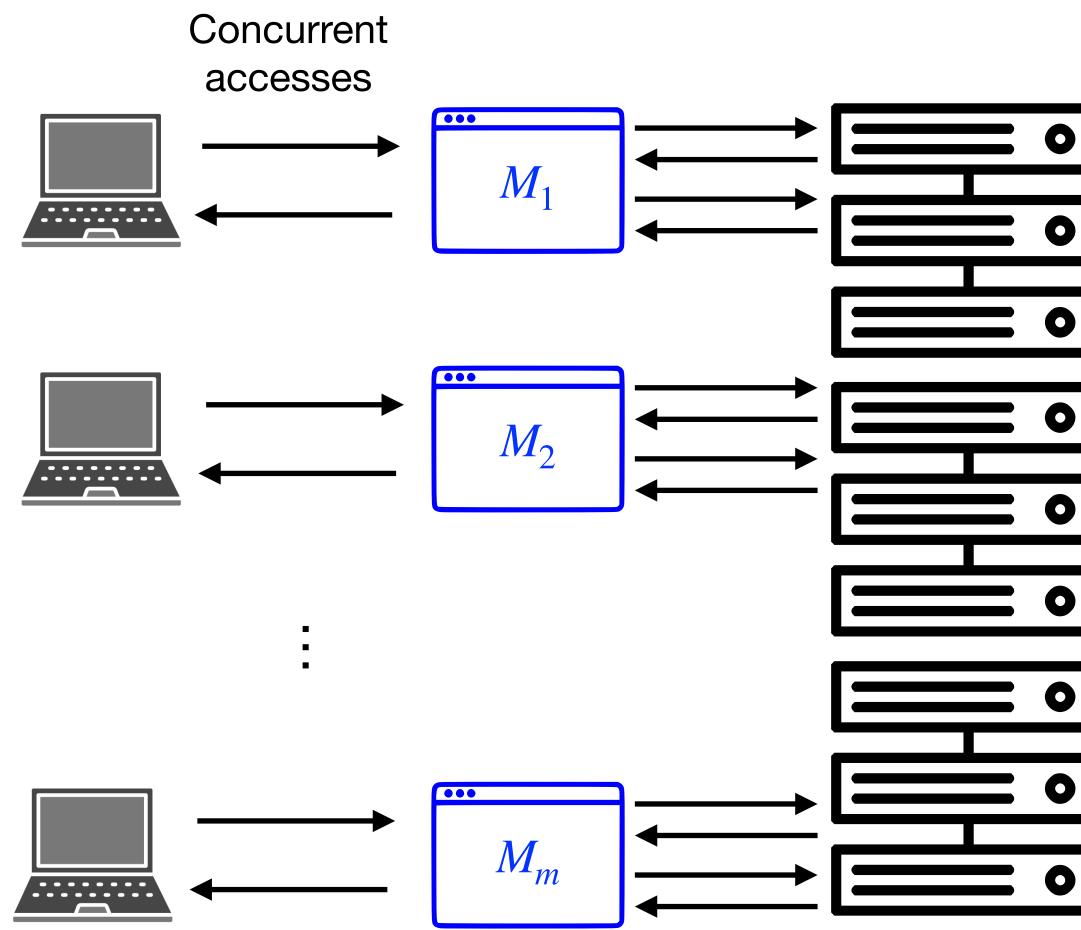

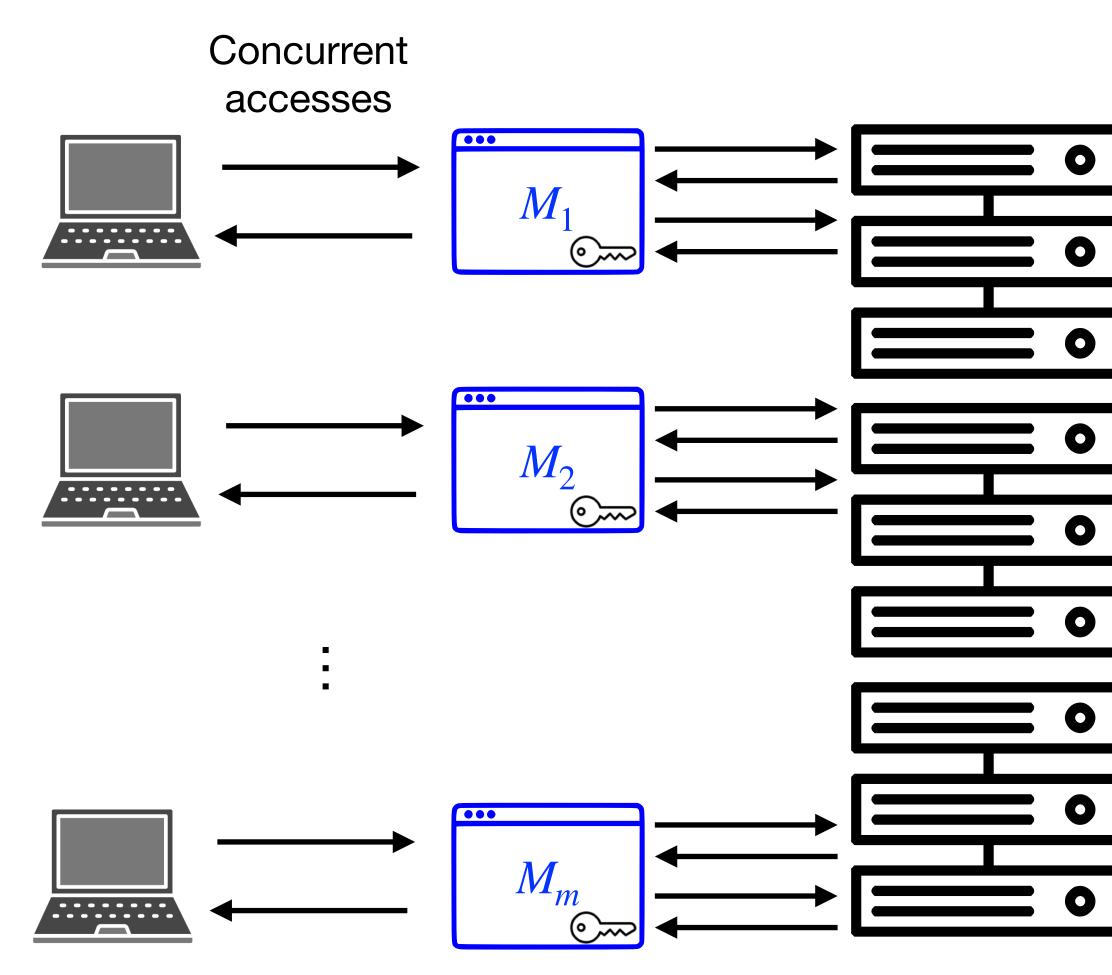

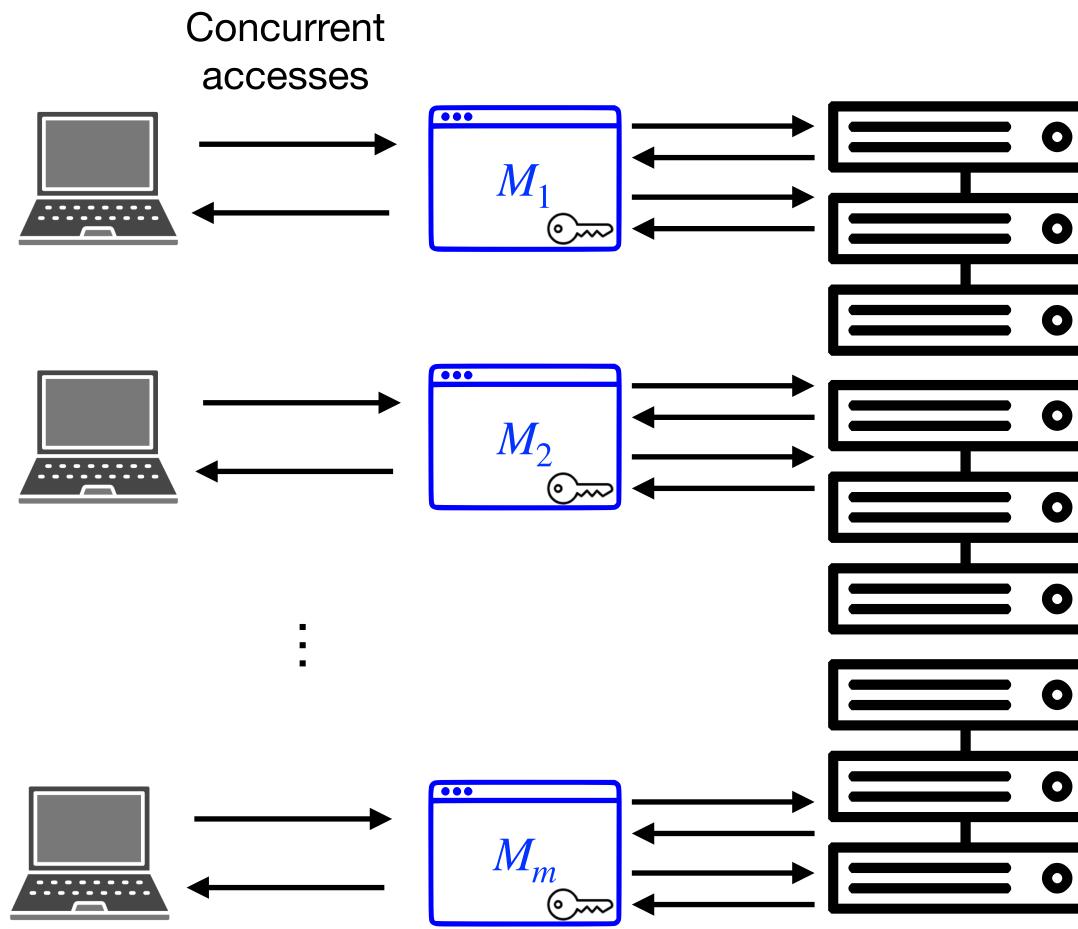

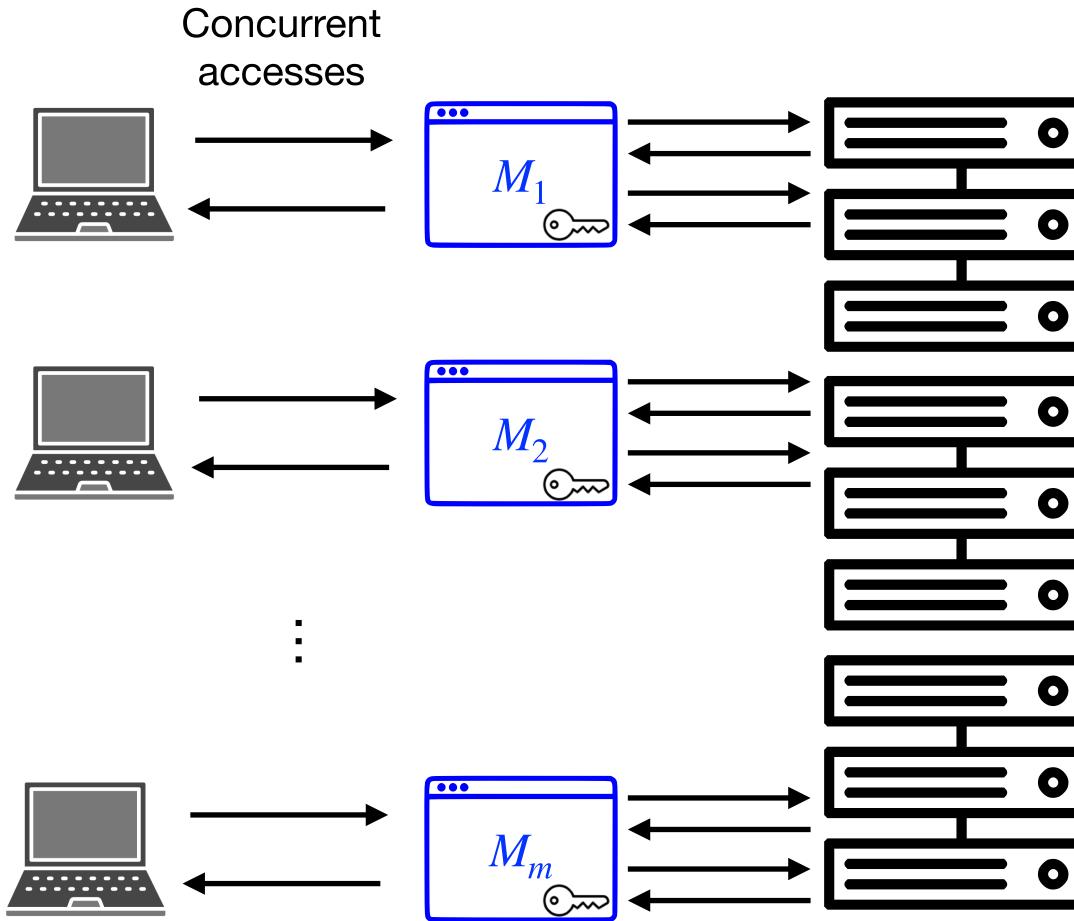

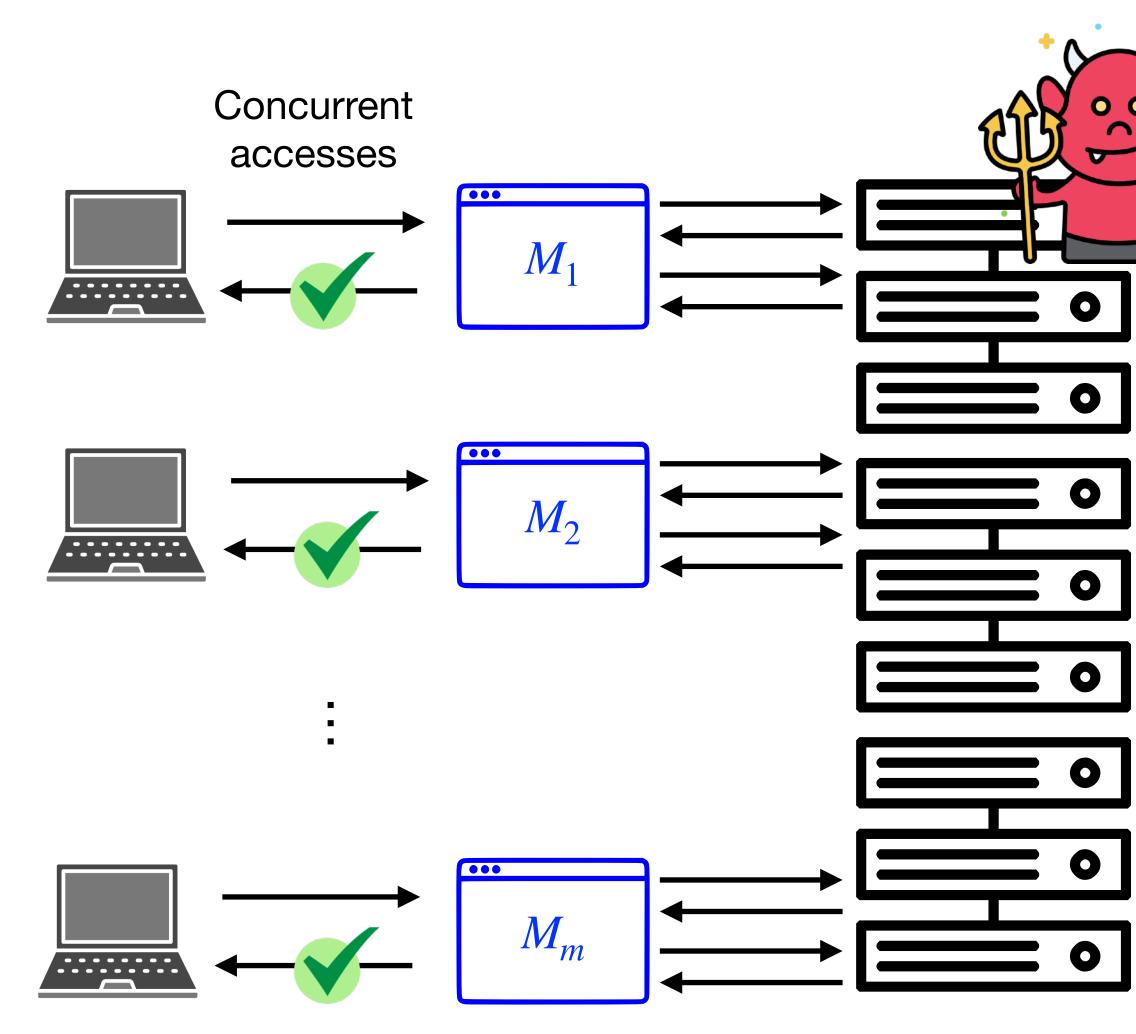

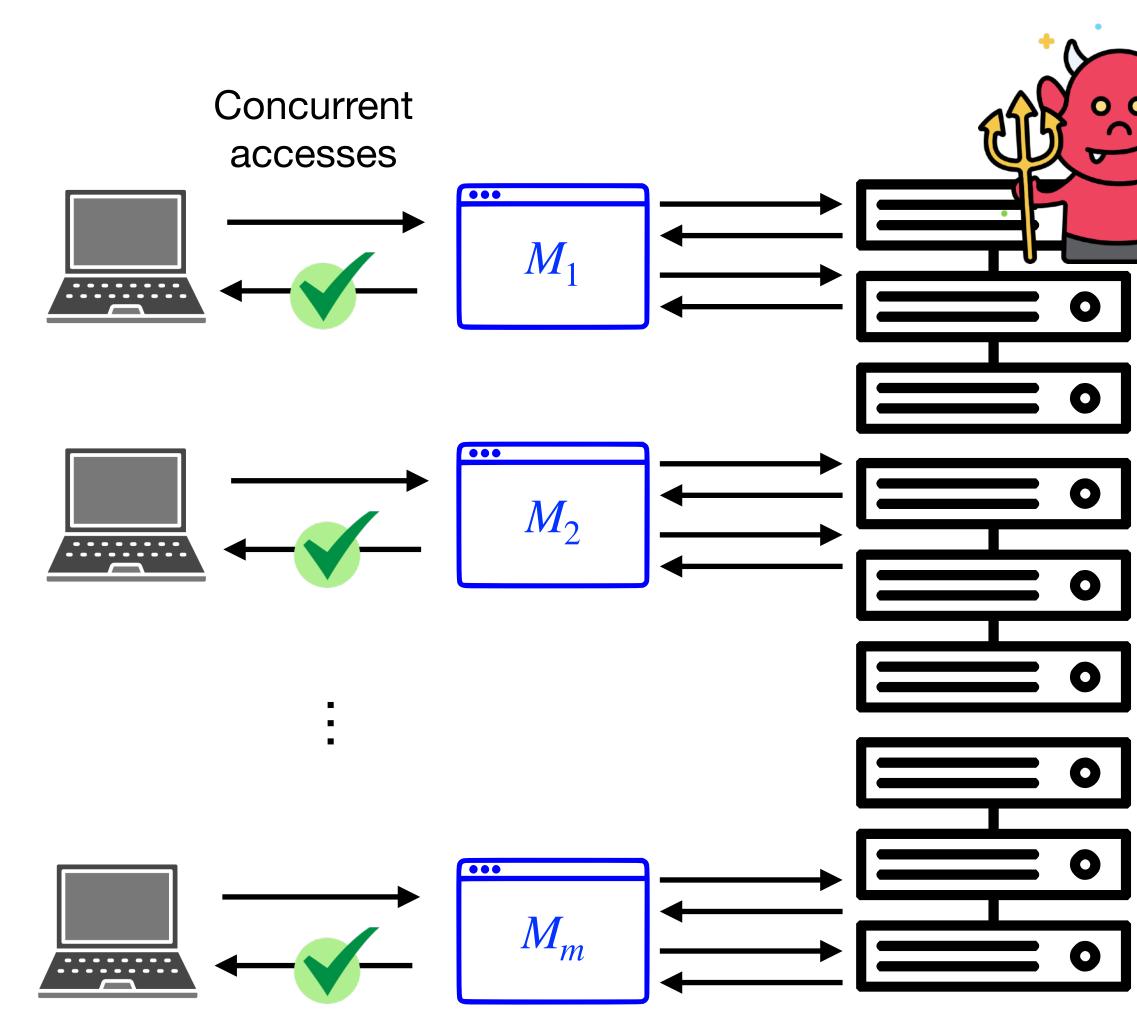

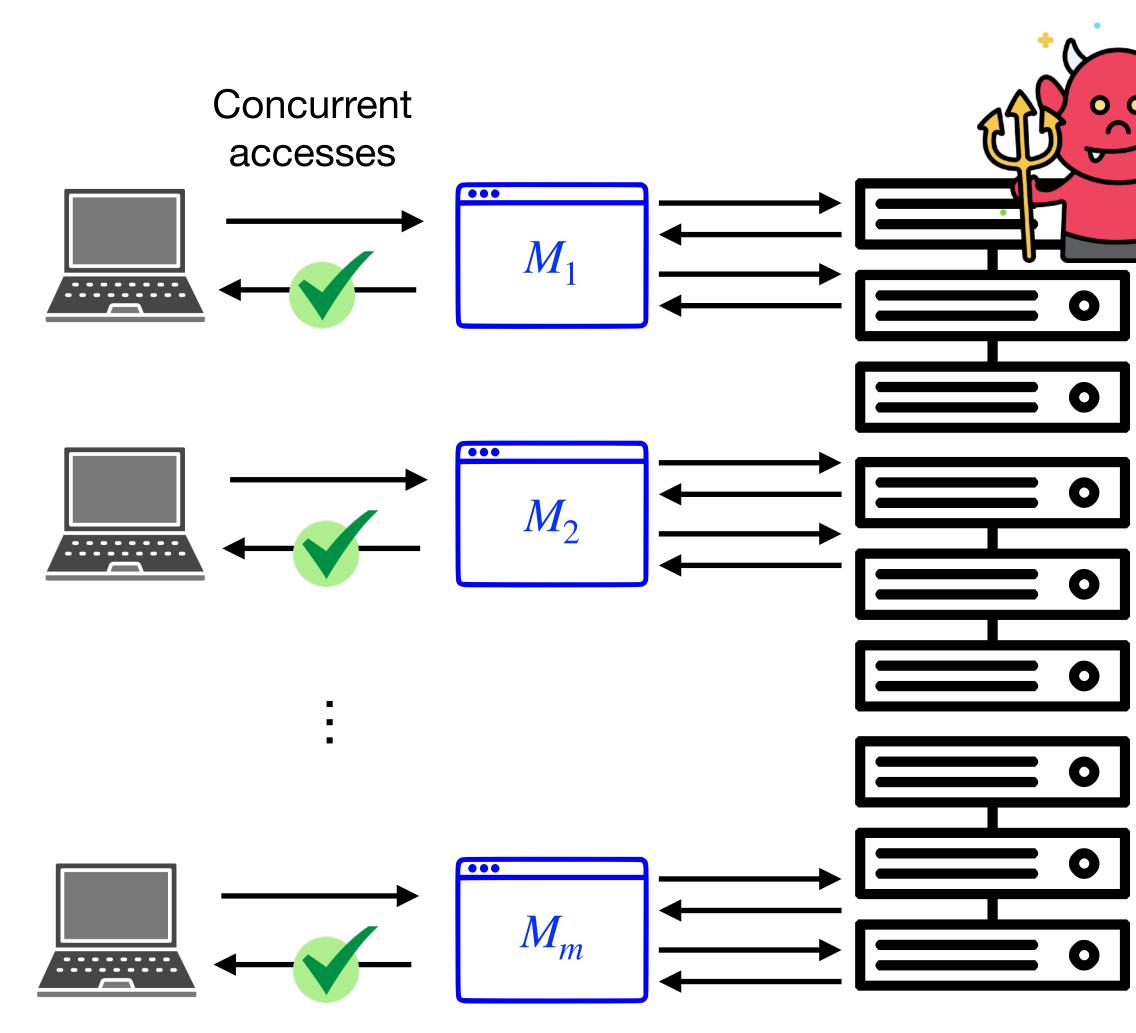

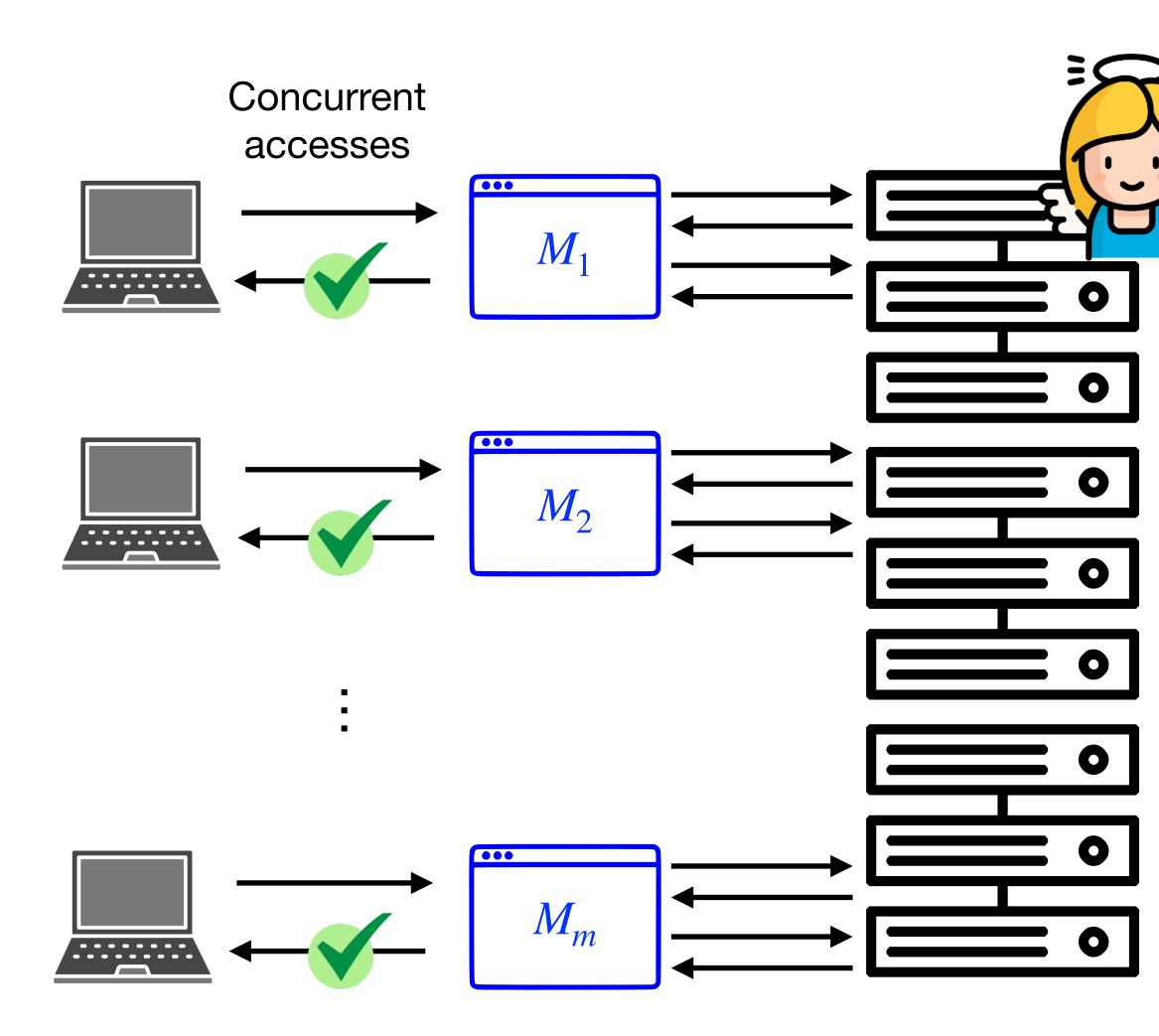

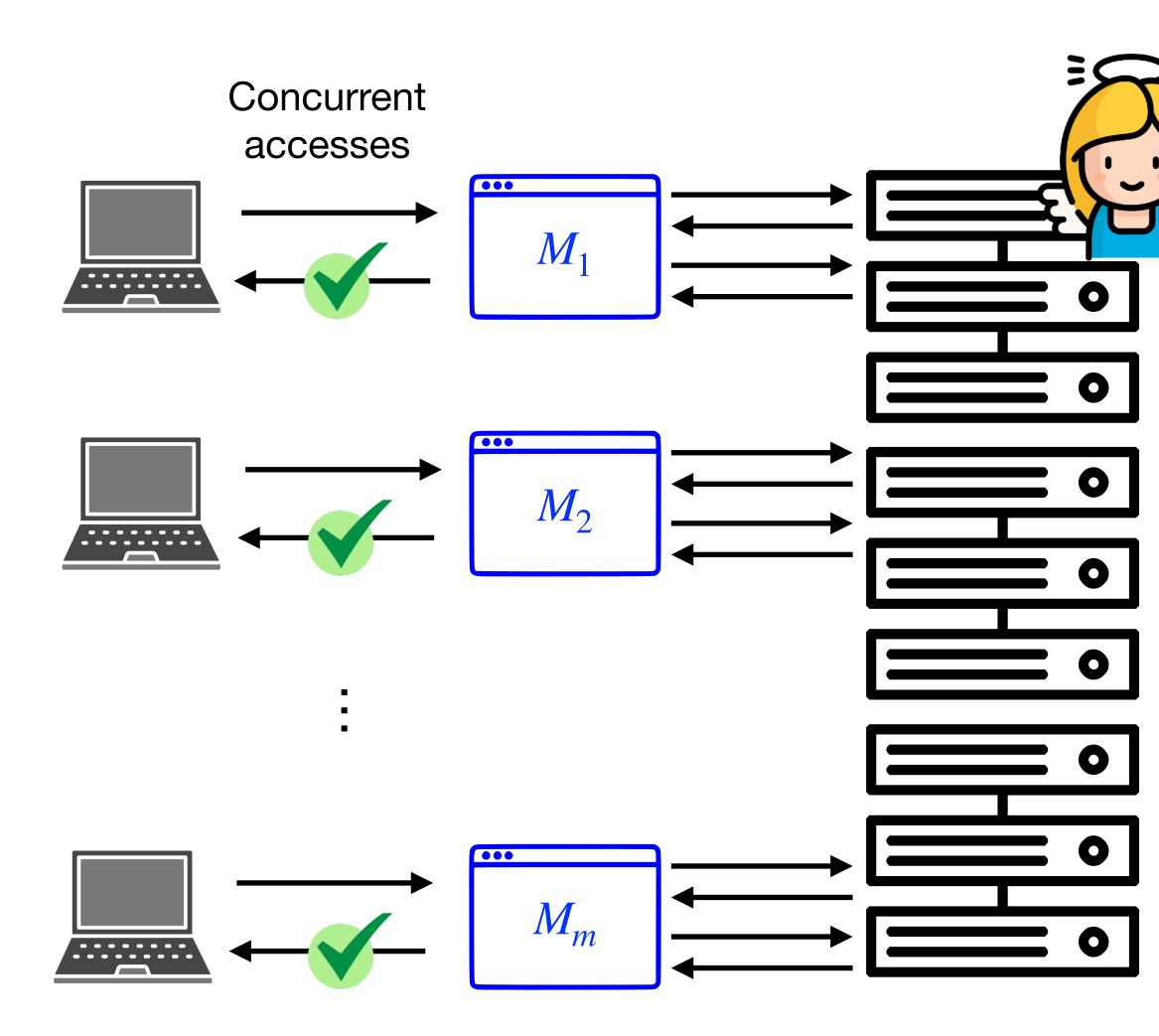

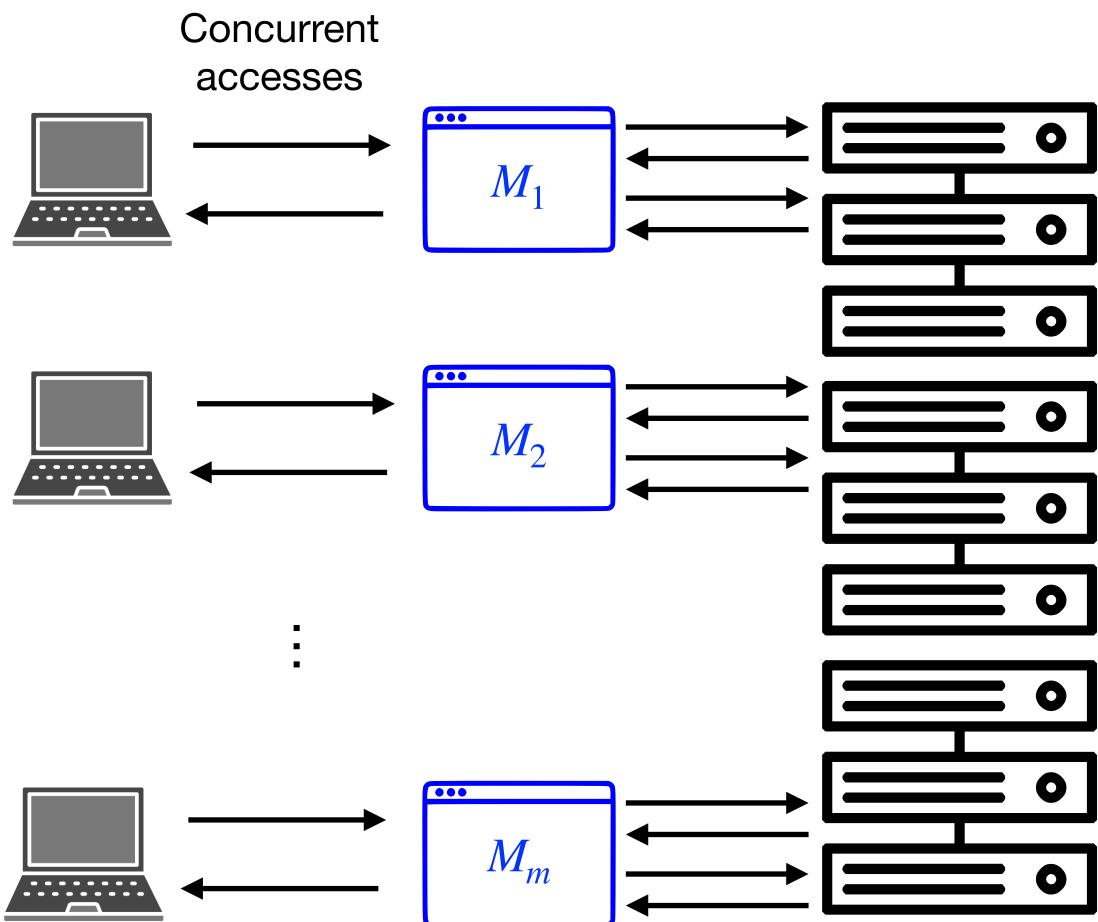

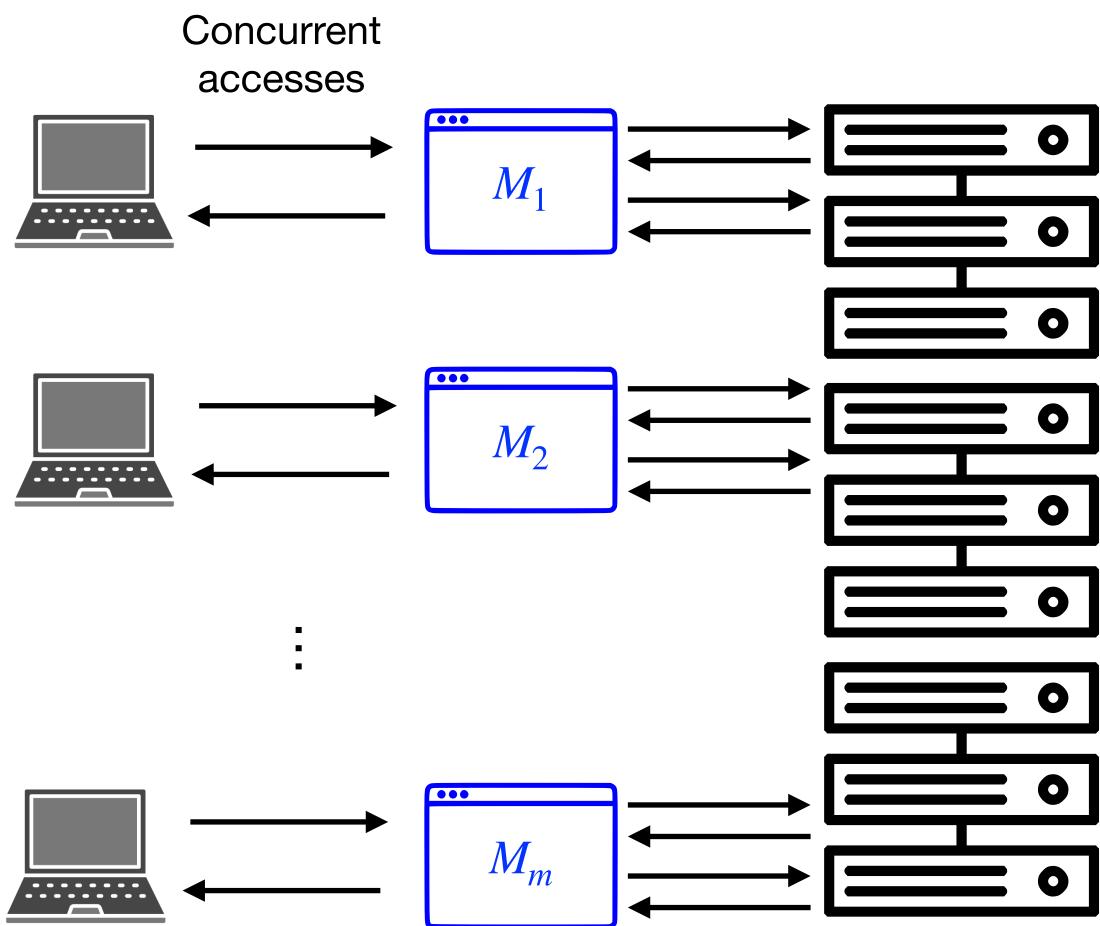

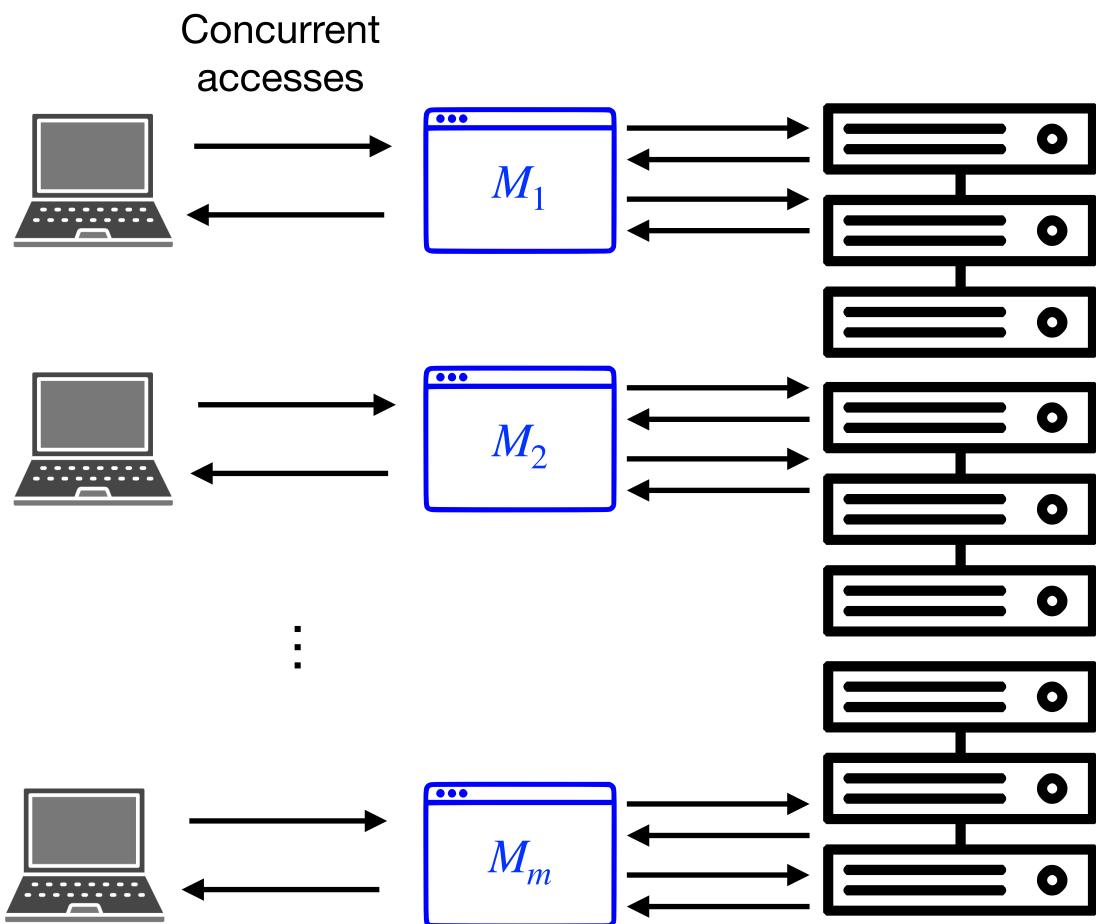

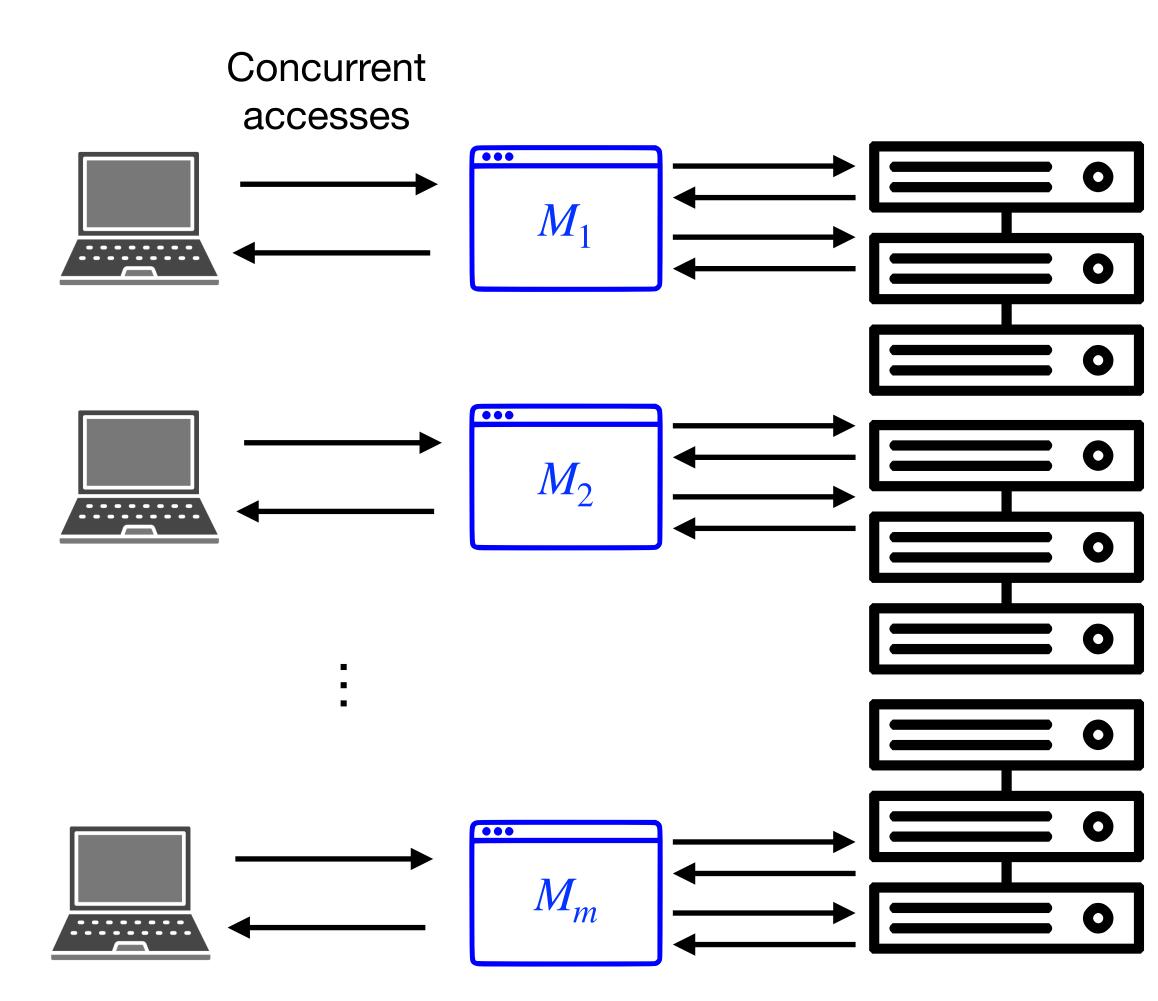

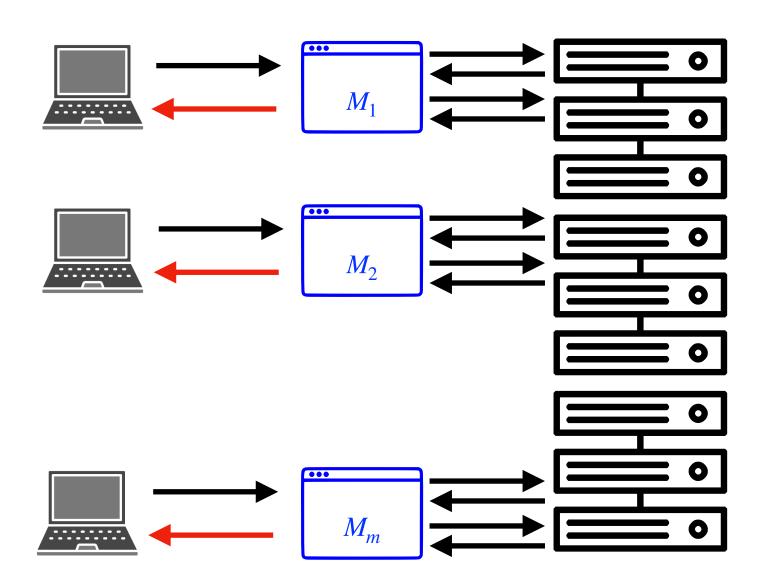

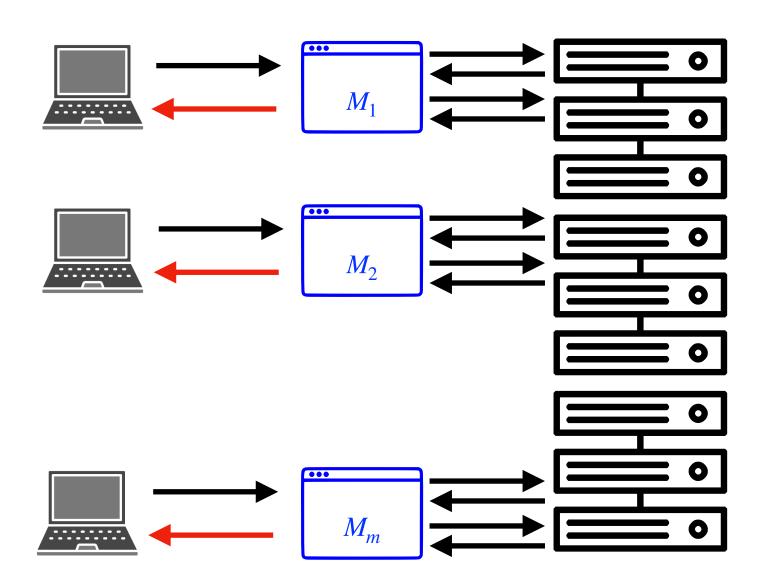

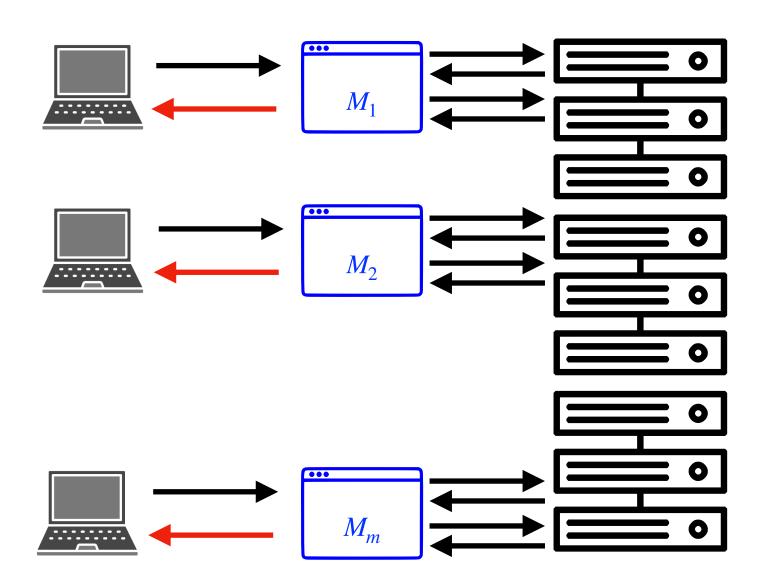

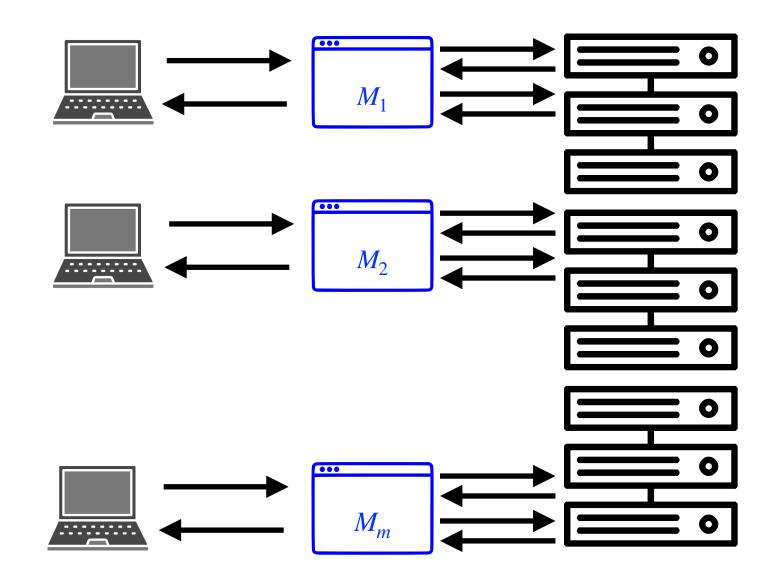

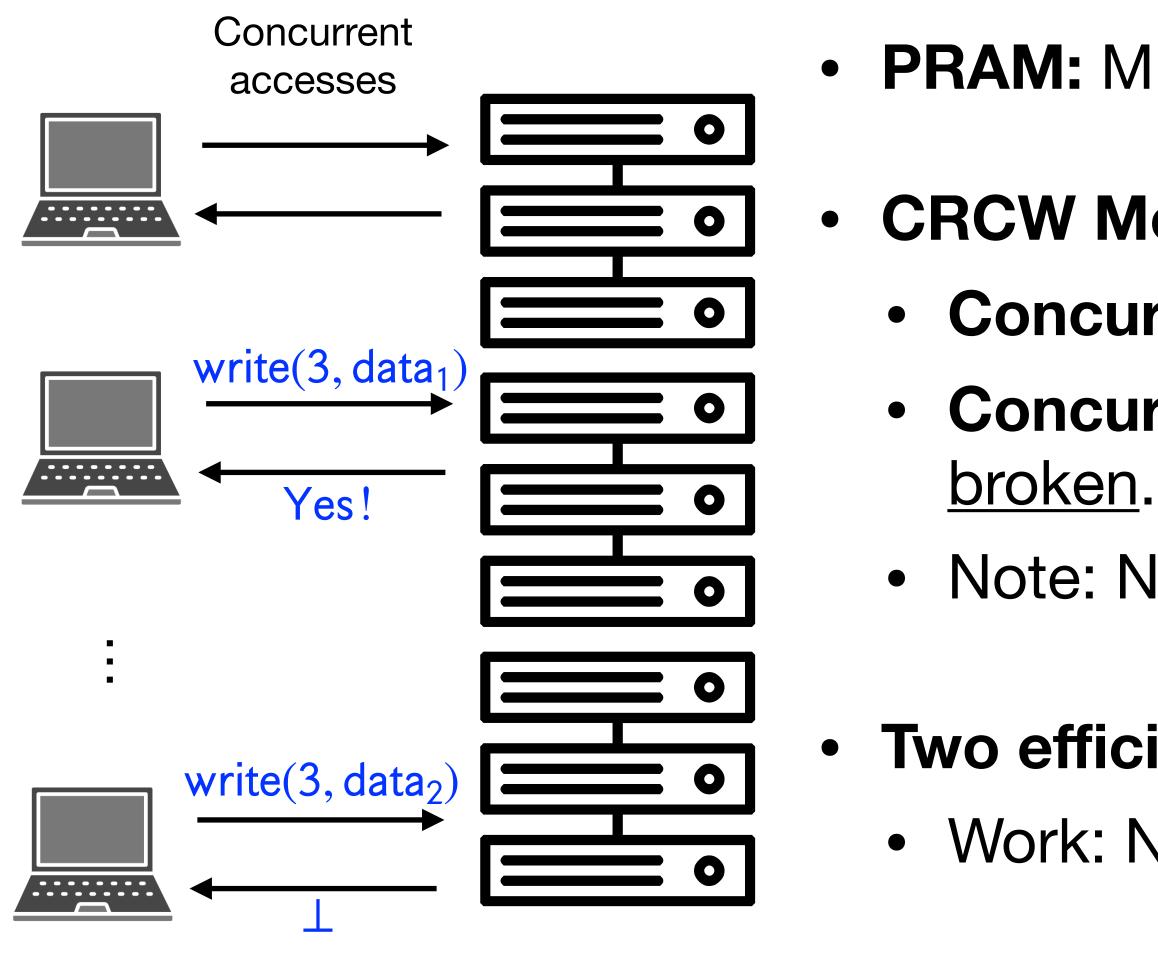

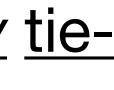

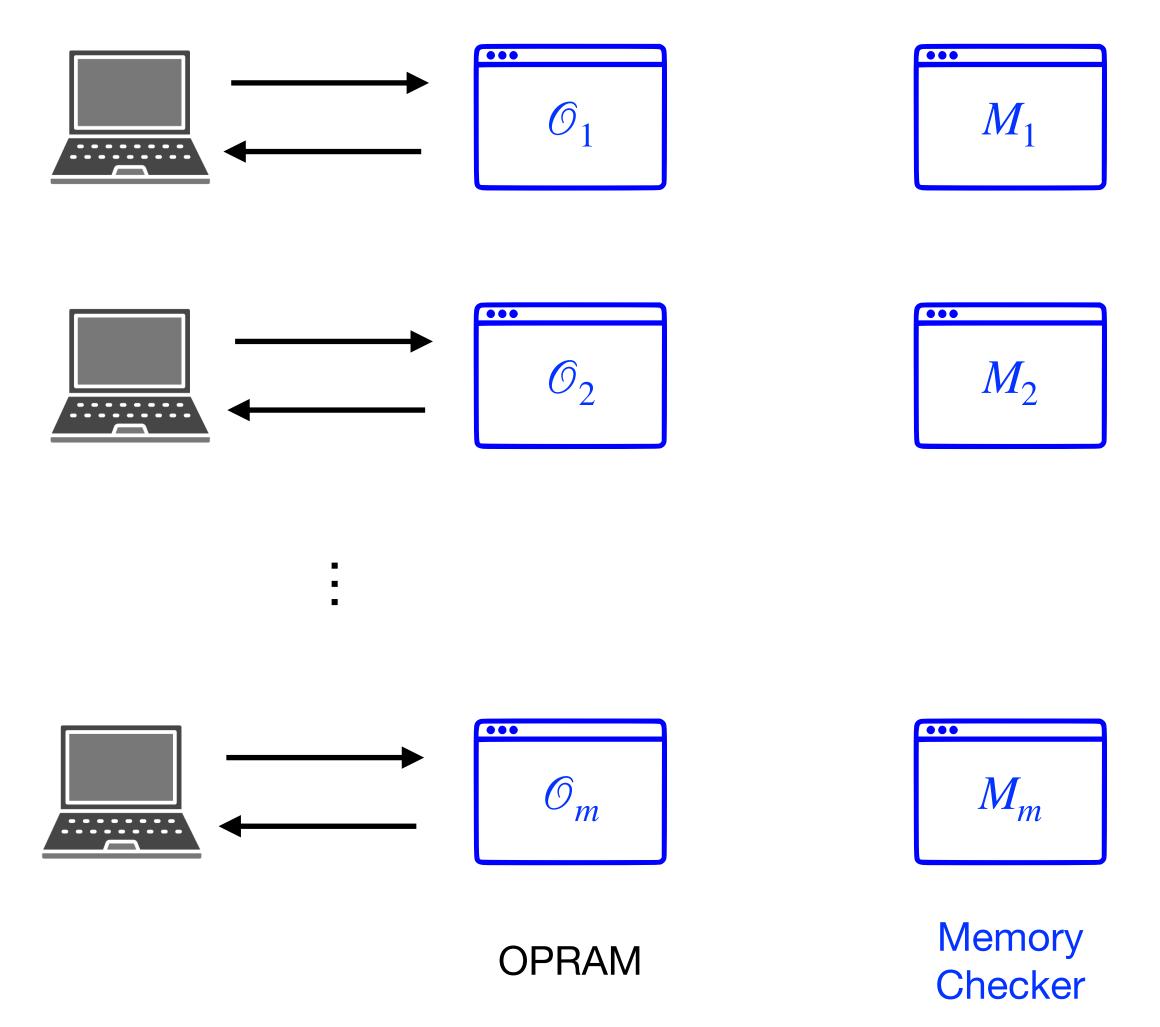

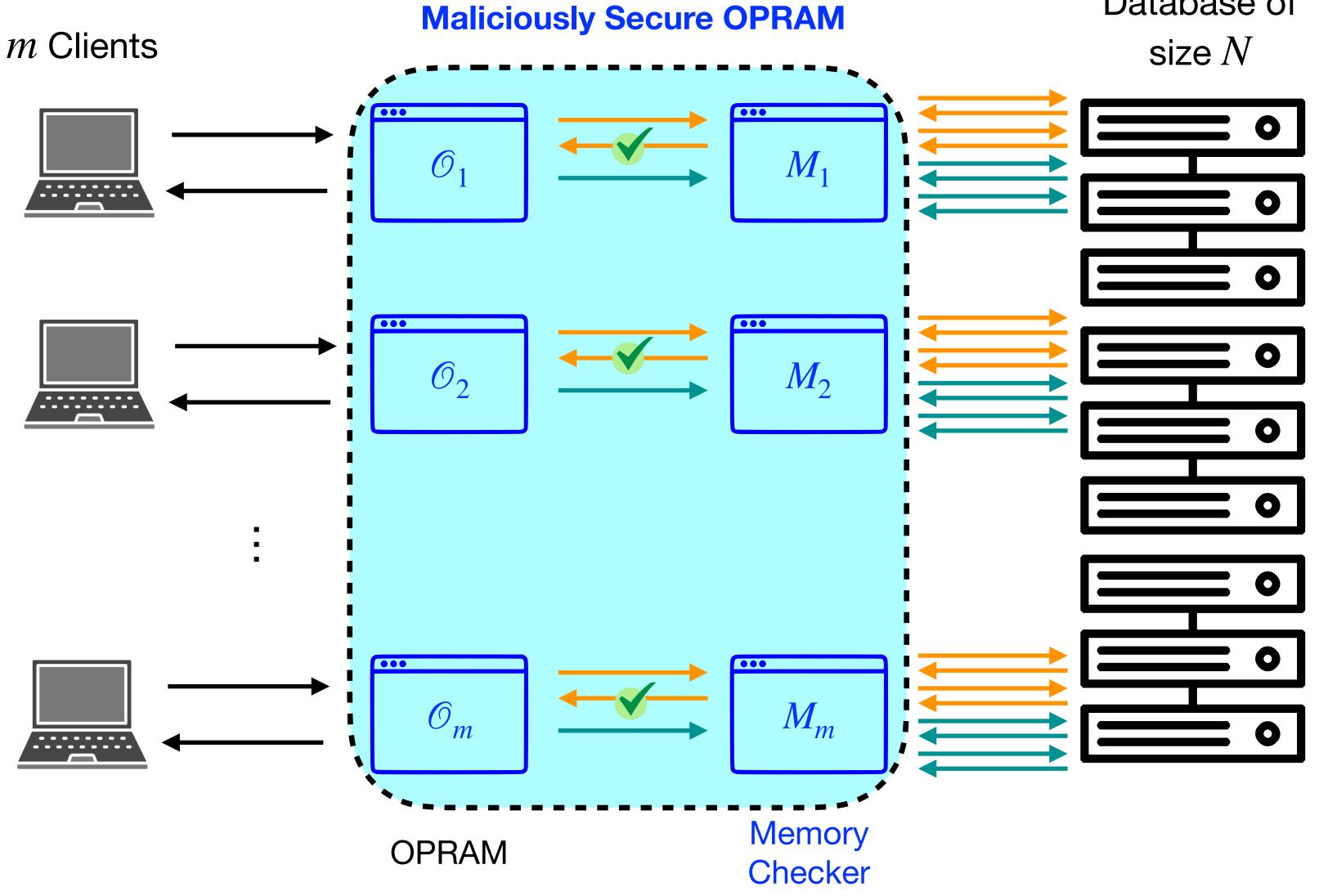

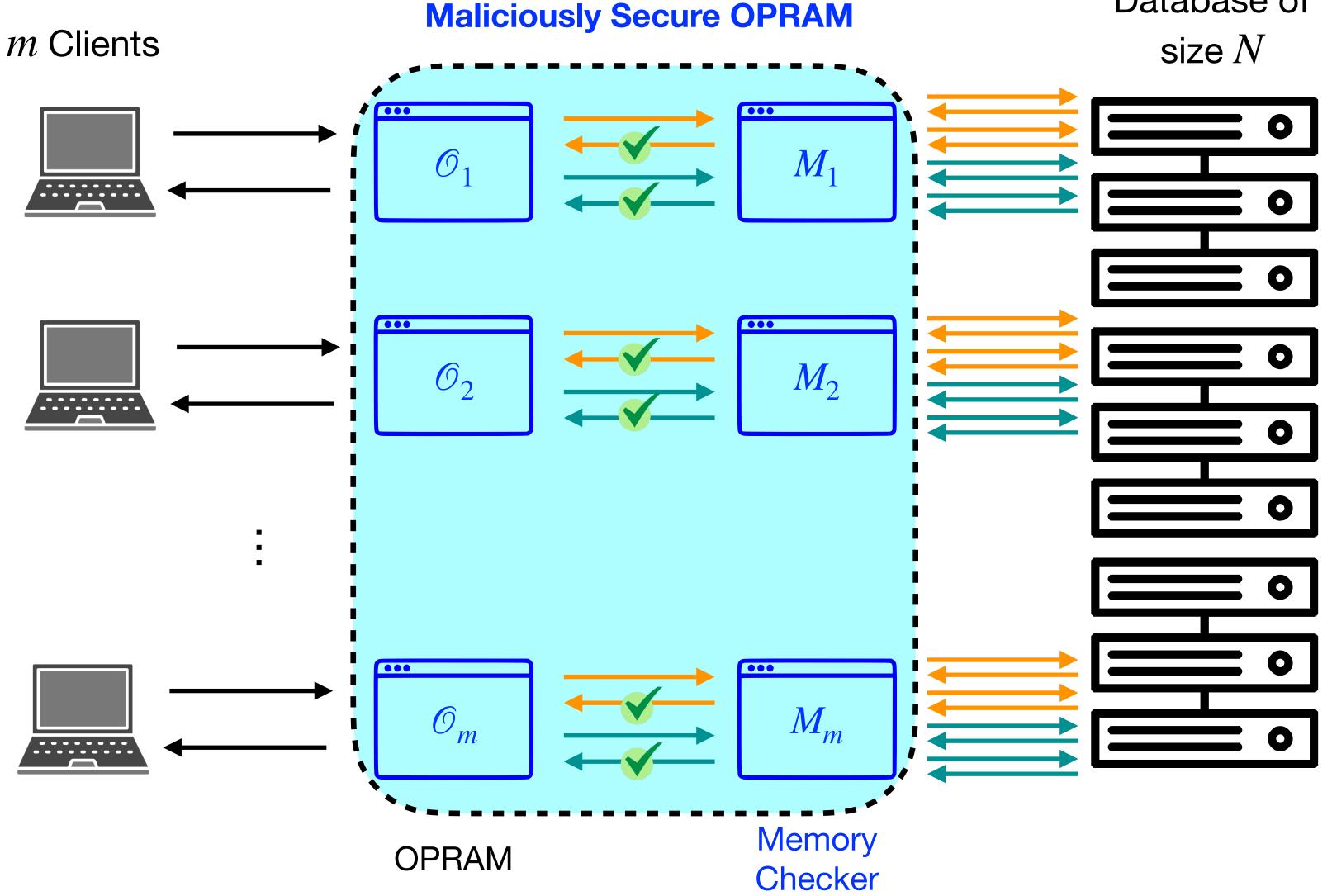

*m* Clients

Database of size N

*m* Clients

Database of size N

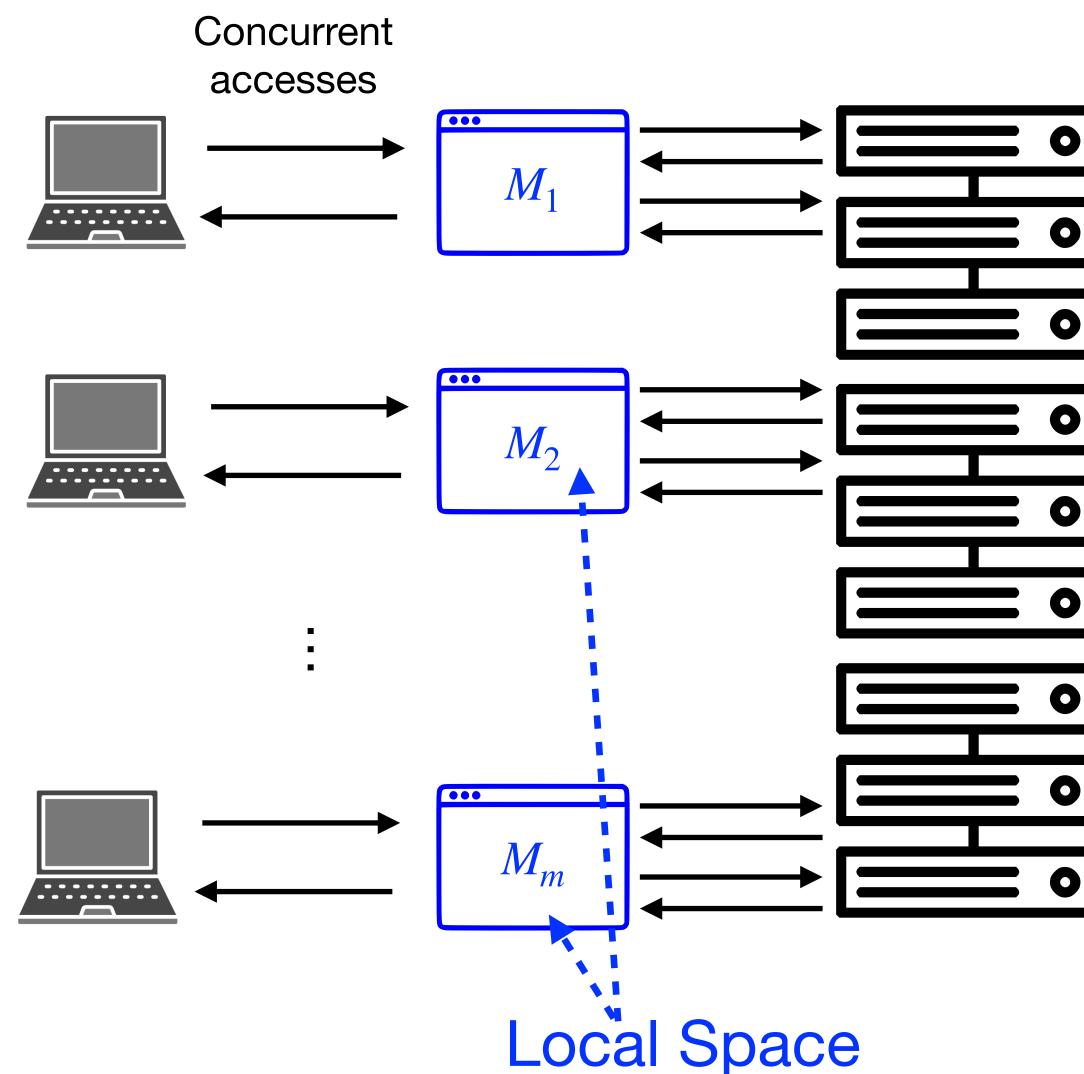

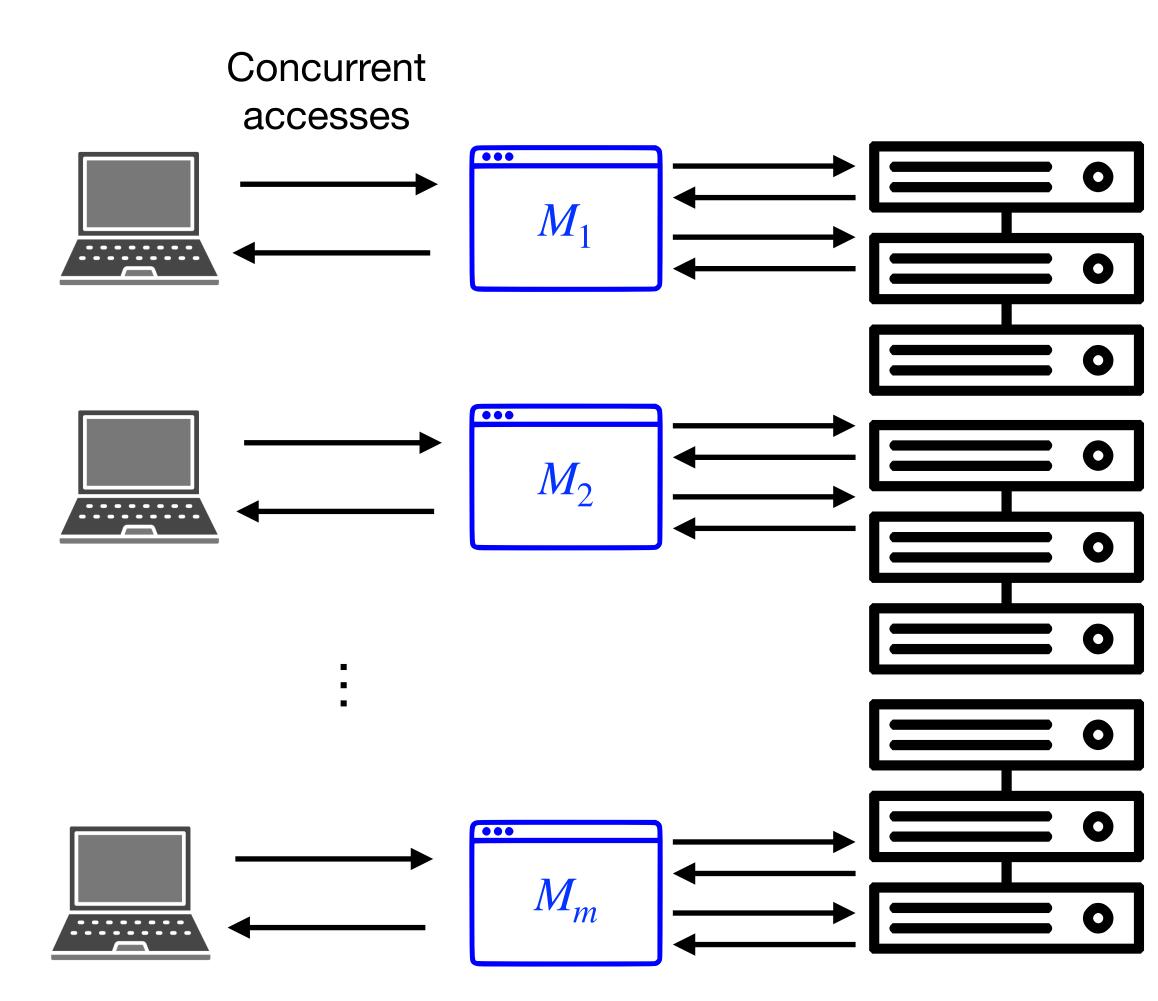

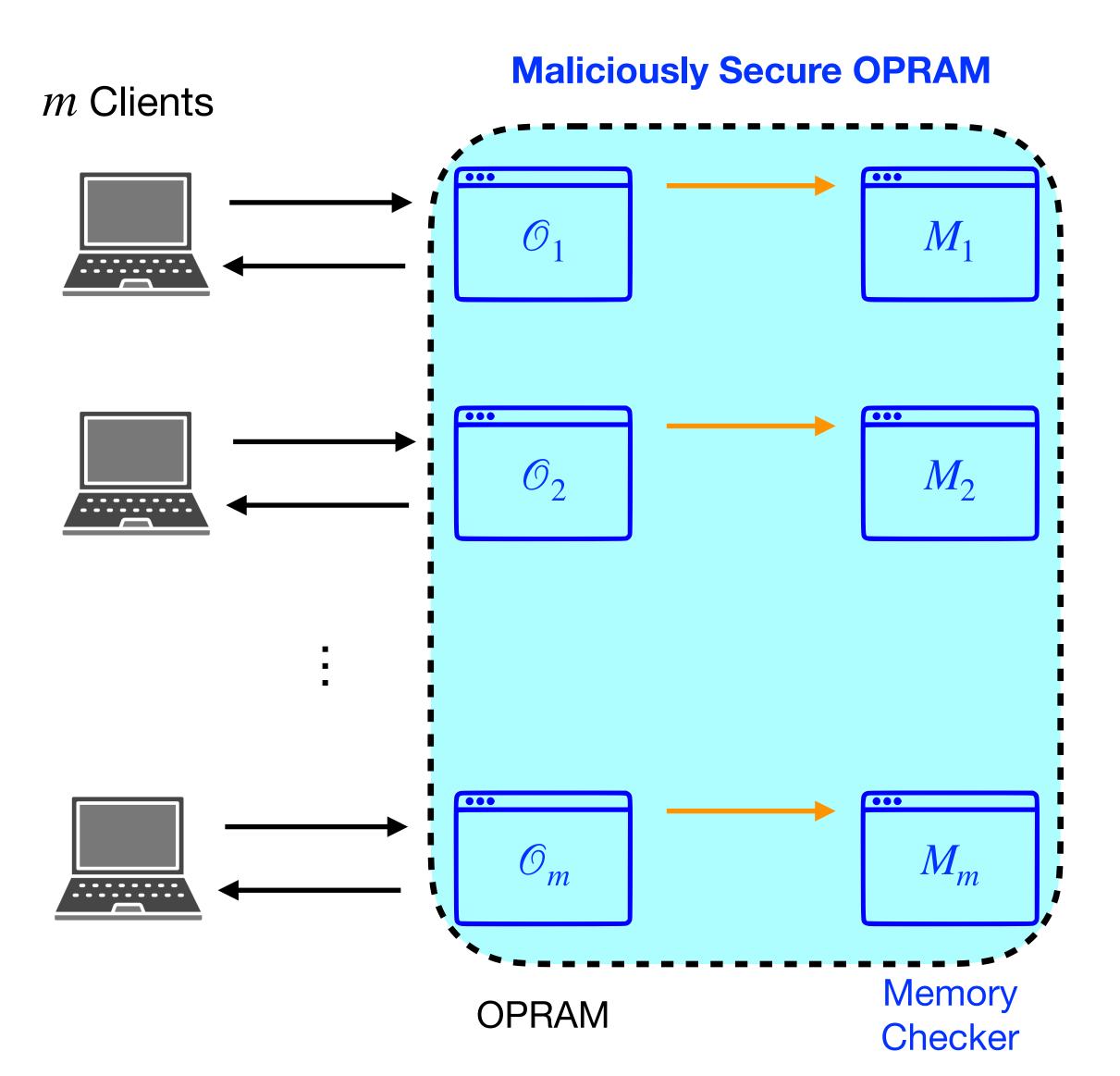

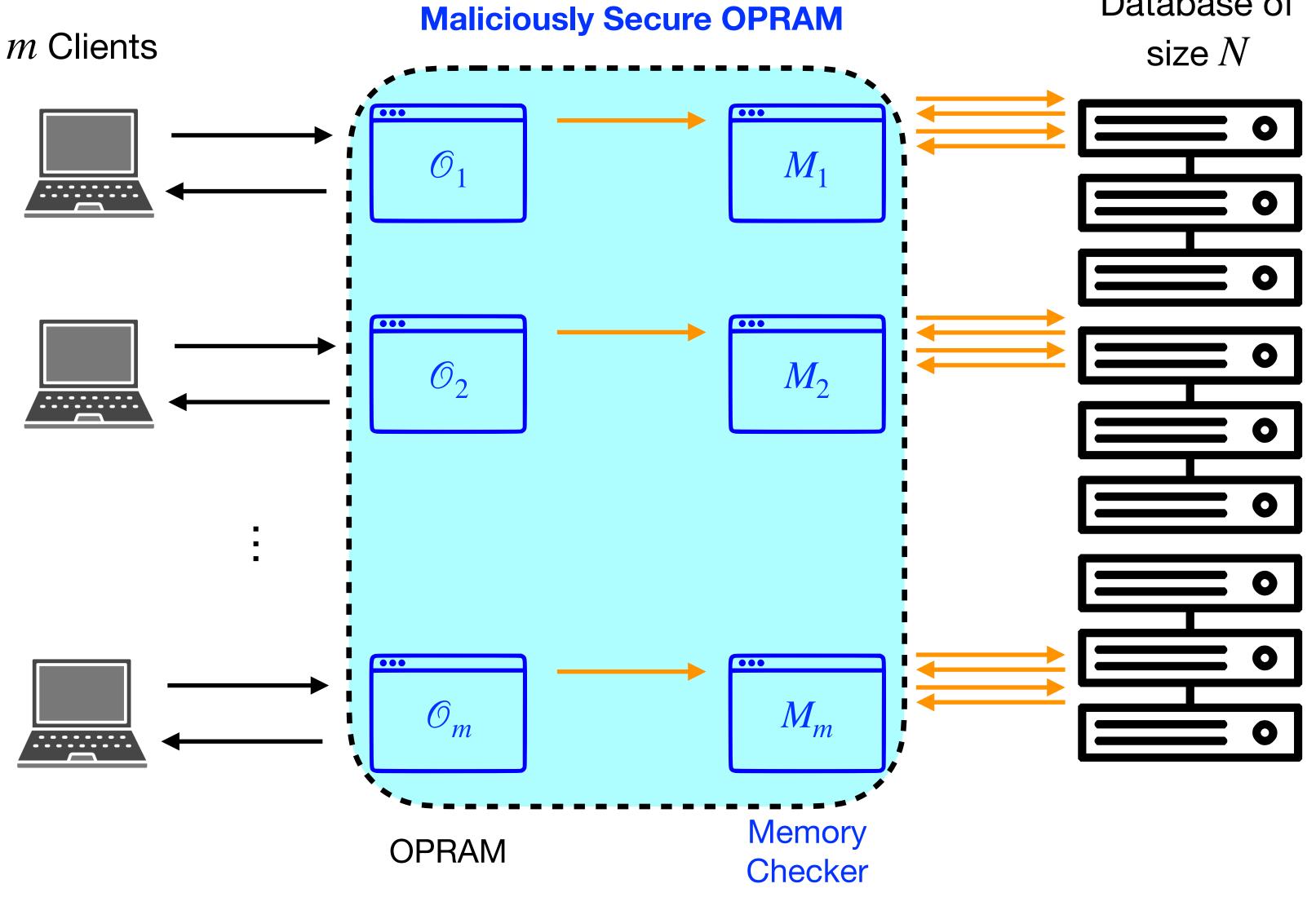

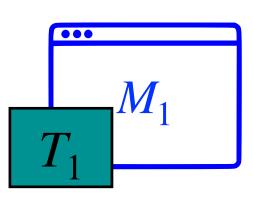

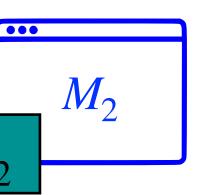

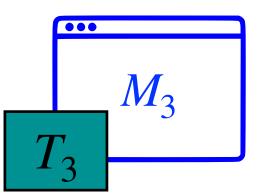

We now define a notion of **memory** checking for parallel RAMs.

*m* Clients

Database of size N

We now define a notion of **memory** checking for parallel RAMs.

**Set-up phase:**

*m* Clients

Database of size N

We now define a notion of **memory** checking for parallel RAMs.

**Set-up phase:**

•  $\{M_i\}$  initialize their states together.

*m* Clients

Database of size N

We now define a notion of **memory** checking for parallel RAMs.

**Set-up phase:**

- $\{M_i\}$  initialize their states together.

- •No *direct* communication after (except through the server).

*m* Clients

Database of size N

We now define a notion of **memory** checking for parallel RAMs.

Set-up phase:

- $\{M_i\}$  initialize their states together.

- •No *direct* communication after (except through the server).

**Note:** It is possible that the clients have secure channels, but we want to make no assumptions.

#### Memory Checking for Parallel RAMs Concurrent accesses $M_1$ 0 $M_{2}$ $M_m$

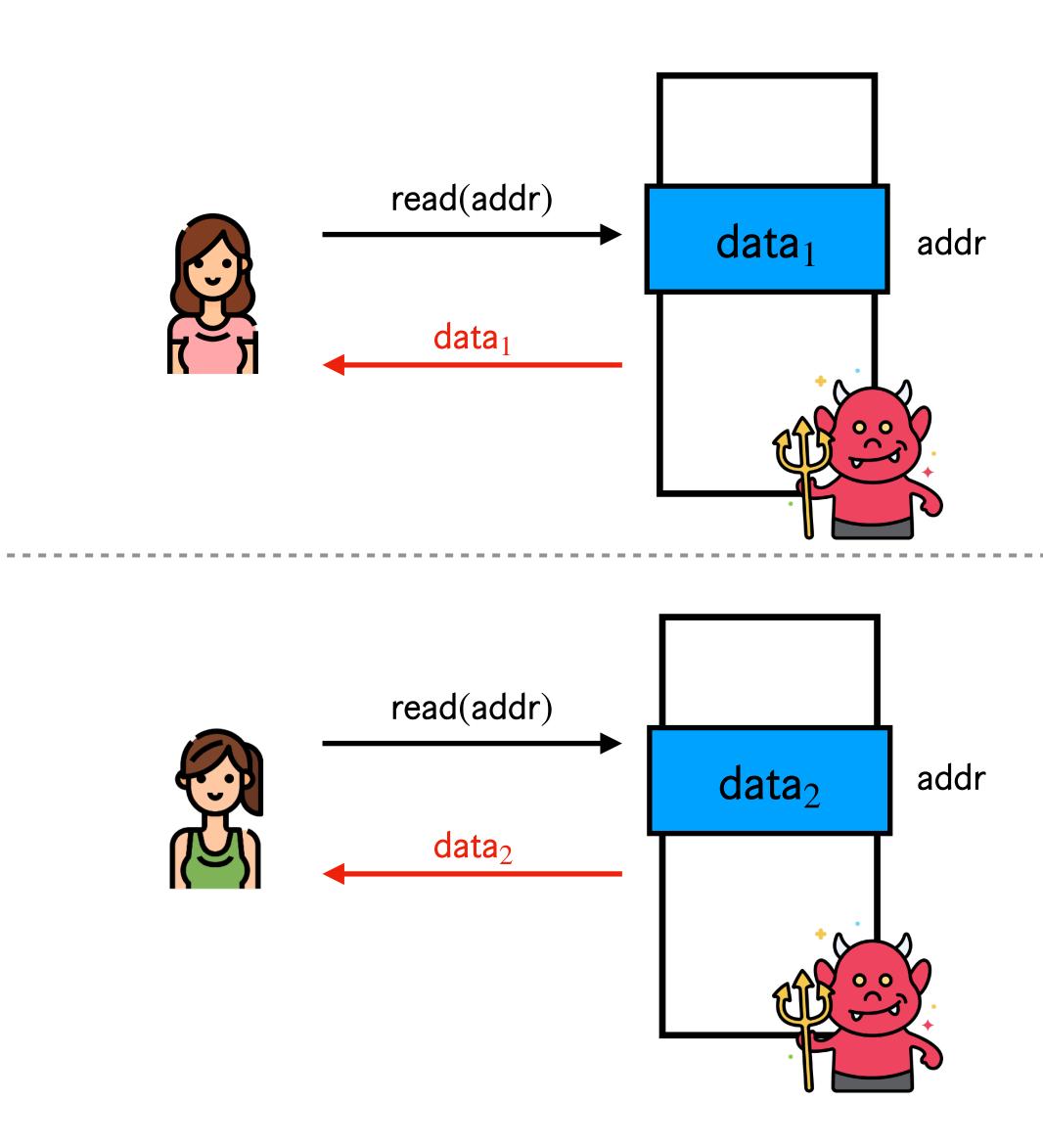

• Correctness: All  $\{M_i\}_i$  send back correct responses, or some  $M_j$  aborts.

- Correctness: All  $\{M_i\}_i$  send back correct responses, or some  $M_j$  aborts.

- All reads are correct

- **Correctness:** All  $\{M_i\}_i$  send back correct responses, or some  $M_j$  aborts.

- All reads are correct

- Concurrent writes are tie-broken (arbitrarily chosen by server)

- **Correctness:** All  $\{M_i\}_i$  send back correct responses, or some  $M_j$ aborts.

- All reads are correct

- Concurrent writes are tie-broken (arbitrarily chosen by server)

- Correctness: All  $\{M_i\}_i$  send back correct responses, or some  $M_j$  aborts.

- All reads are correct

- Concurrent writes are tie-broken (arbitrarily chosen by server)

- **Completeness:** No  $M_j$  aborts if server is not malicious.

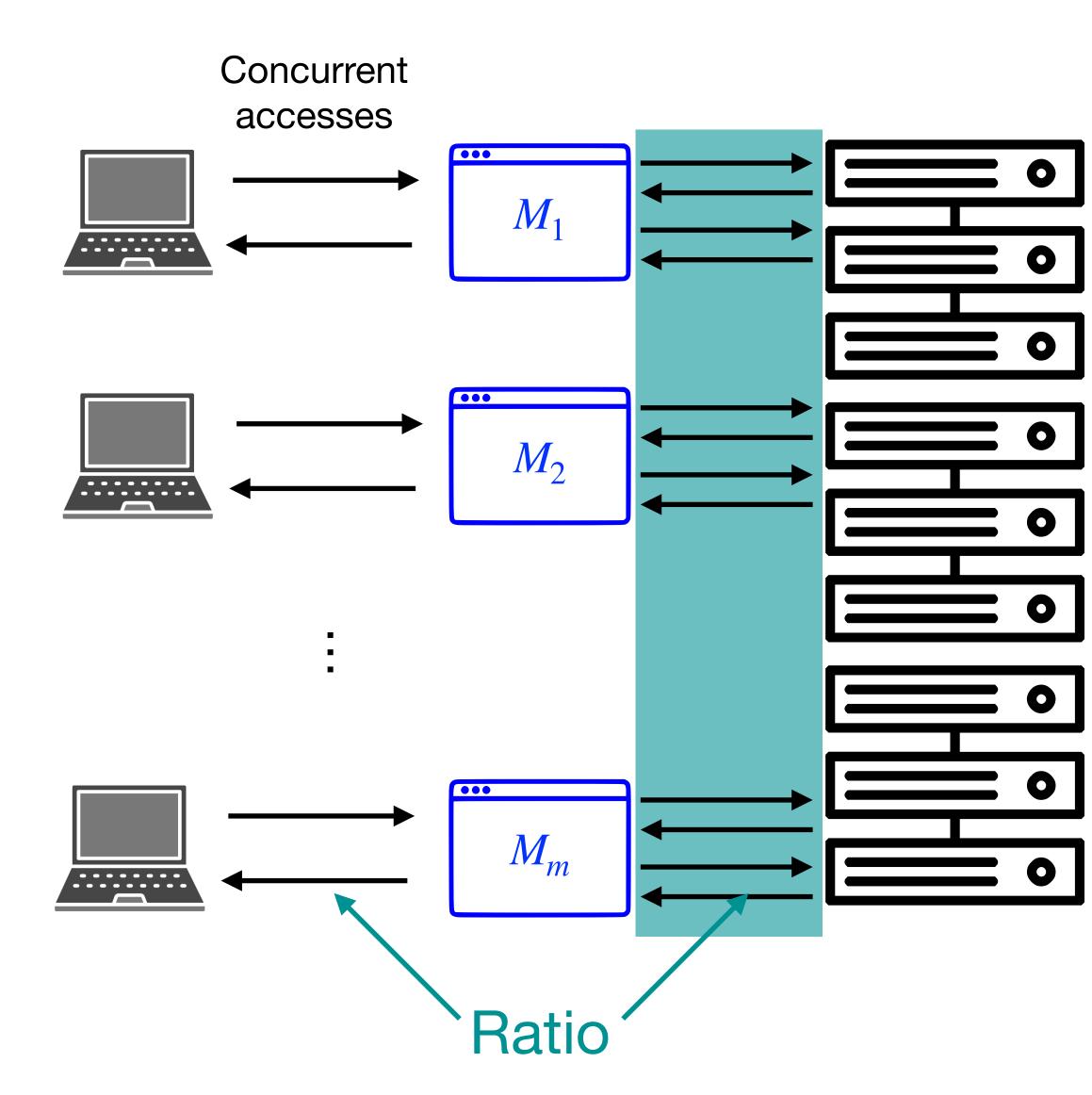

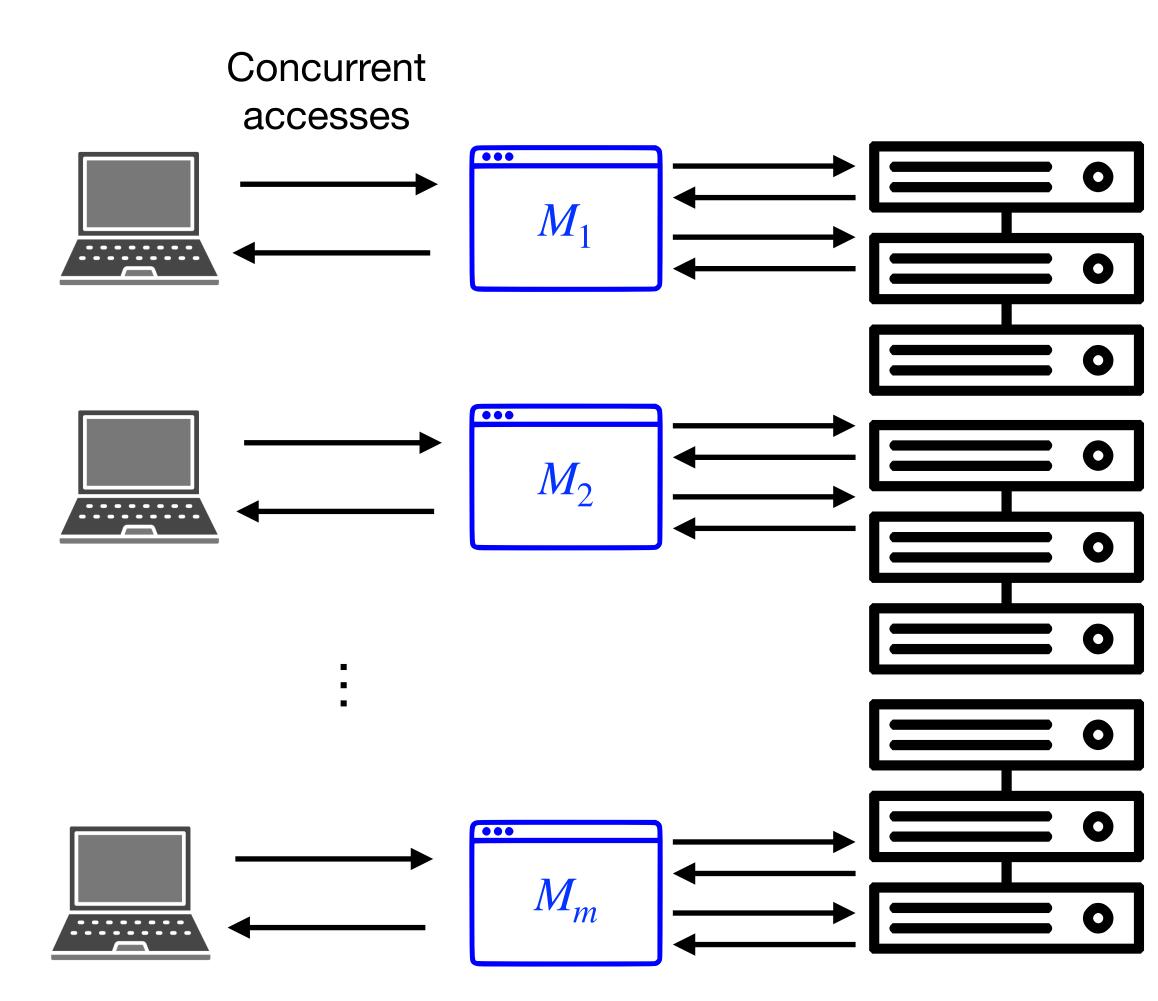

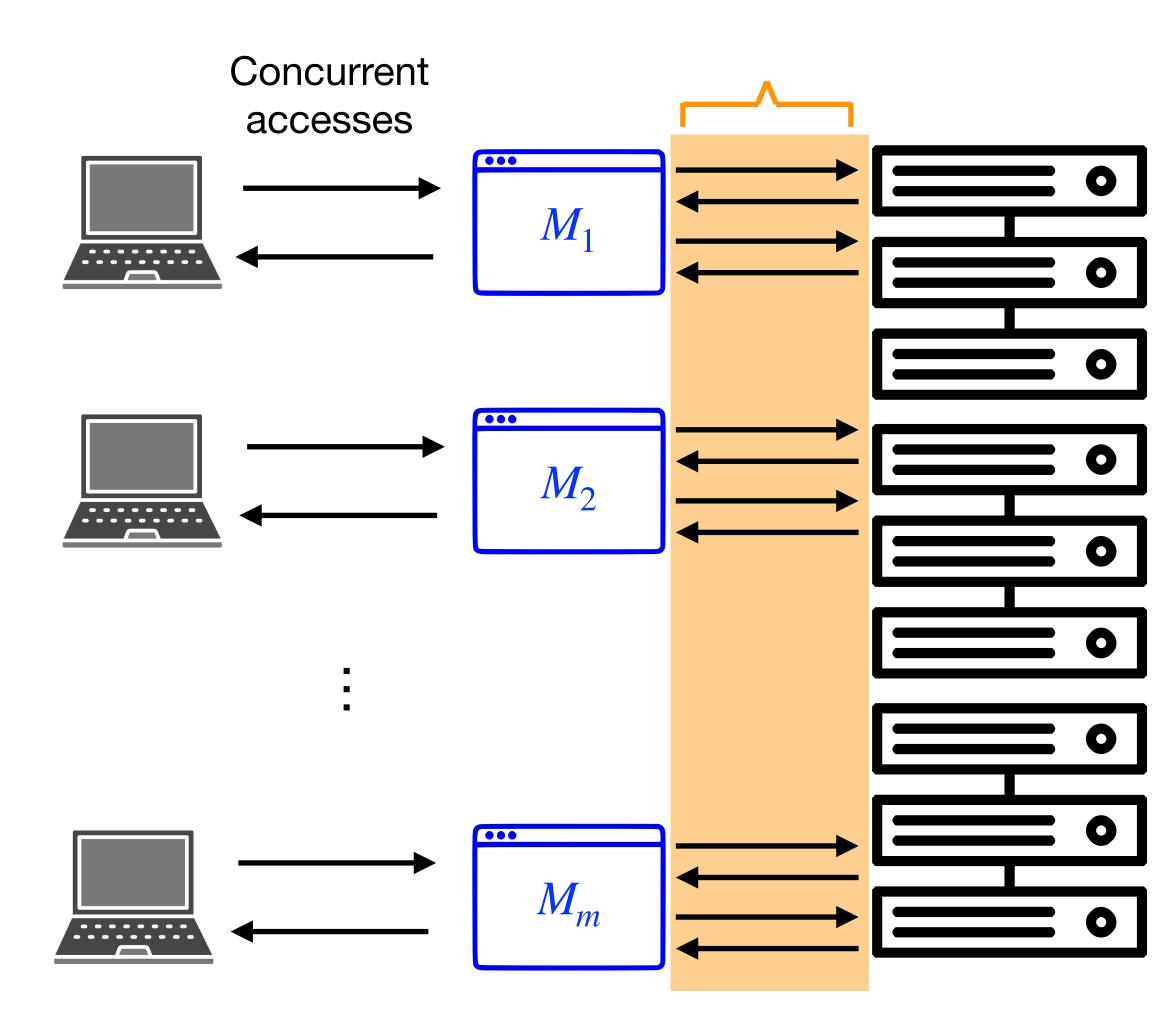

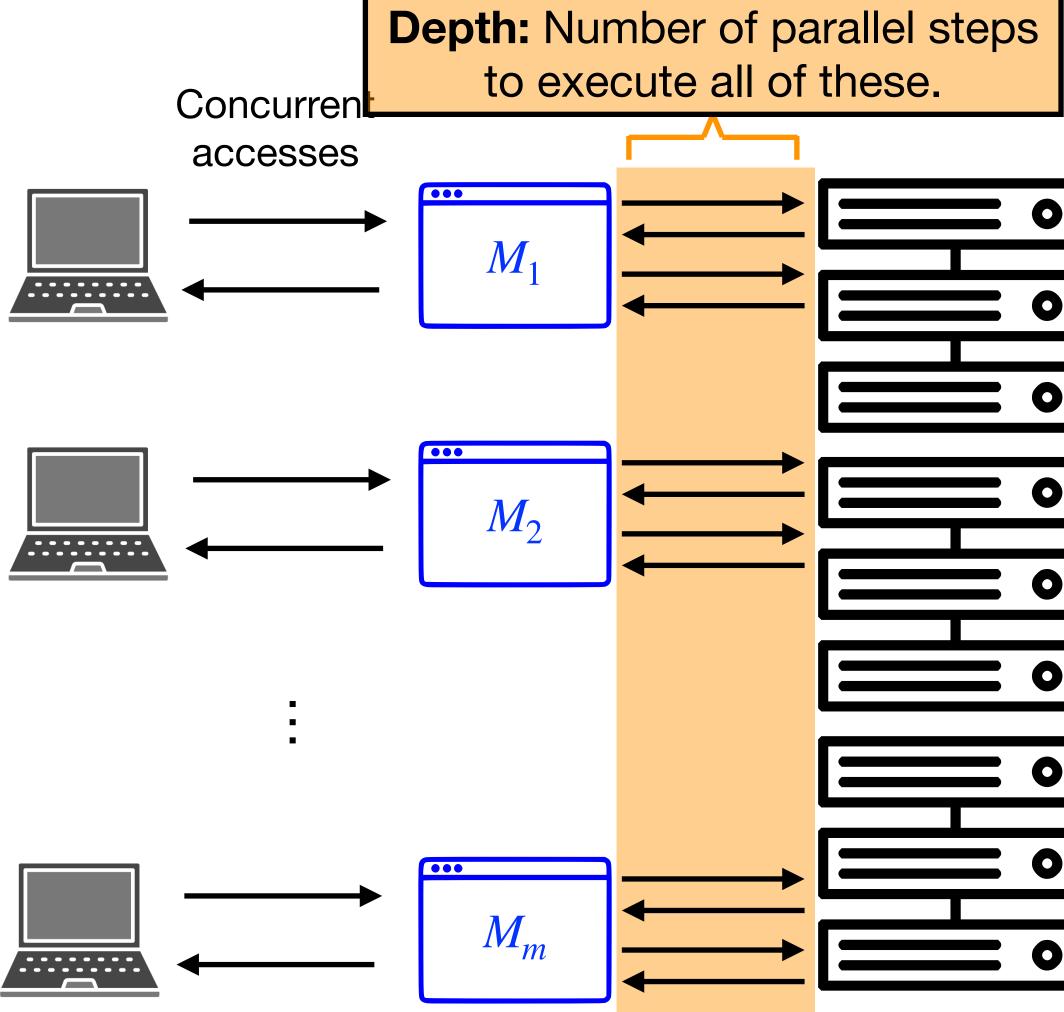

#### **Efficiency metrics**

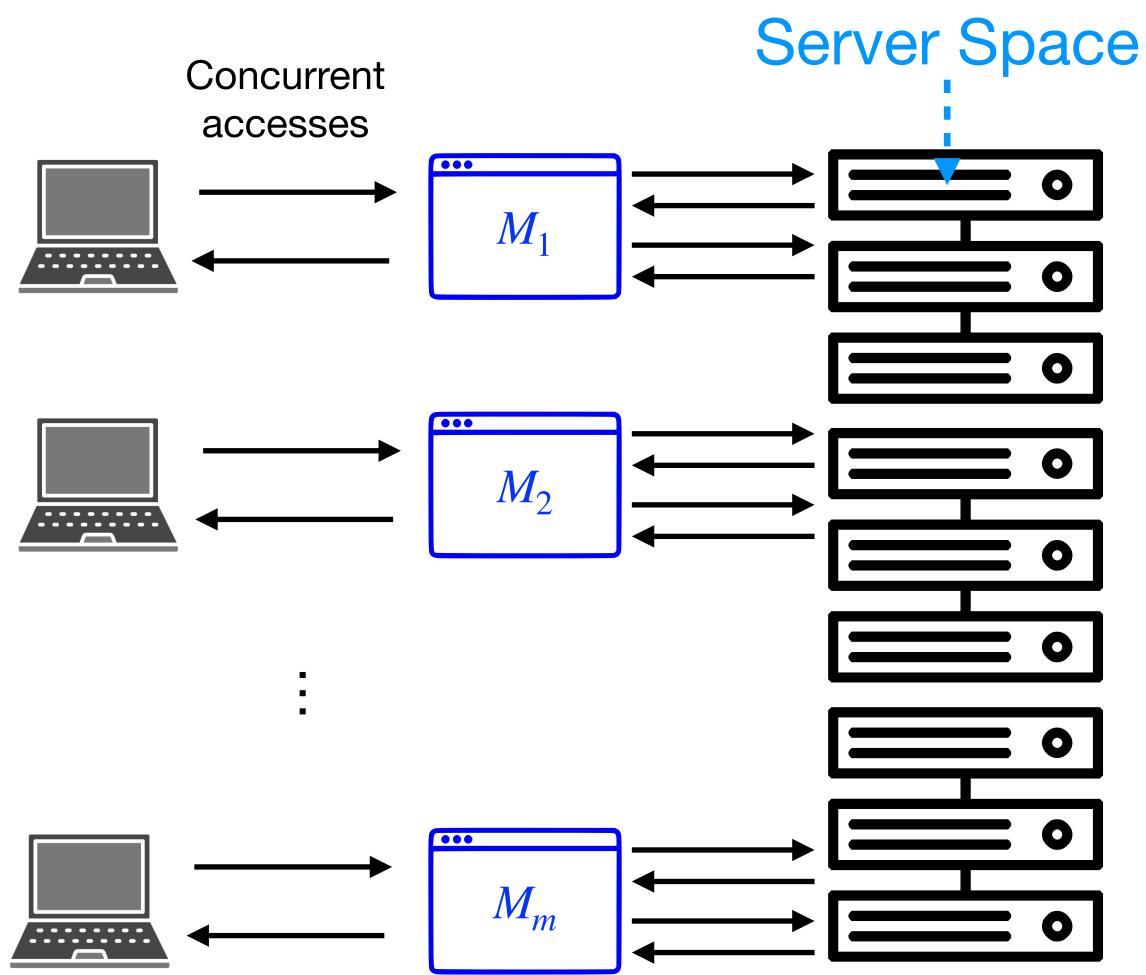

• Local Space: Space per checker. This talk: O(1) words/ $O(\lambda)$  bits.

#### **Efficiency metrics**

• Local Space: Space per checker. This talk: O(1) words/ $O(\lambda)$  bits.

- Local Space: Space per checker. This talk: O(1) words/ $O(\lambda)$  bits.

- Server Space: Server storage size. This talk: O(N) words.

- Local Space: Space per checker. This talk: O(1) words/ $O(\lambda)$  bits.

- Server Space: Server storage size. This talk: O(N) words.

- Local Space: Space per checker. This talk: O(1) words/ $O(\lambda)$  bits.

- Server Space: Server storage size. This talk: O(N) words.

- Work blowup: Ratio of server accesses per underlying PRAM access.

- Local Space: Space per checker. This talk: O(1) words/ $O(\lambda)$  bits.

- Server Space: Server storage size. This talk: O(N) words.

- Work blowup: Ratio of server accesses per underlying PRAM access.

- Local Space: Space per checker. This talk: O(1) words/ $O(\lambda)$  bits.

- Server Space: Server storage size. This talk: O(N) words.

- Work blowup: Ratio of server accesses per underlying PRAM access.

- **Depth blowup:** Number of parallel steps to support a single batch of requests.

- Local Space: Space per checker. This talk: O(1) words/ $O(\lambda)$  bits.

- Server Space: Server storage size. This talk: O(N) words.

- Work blowup: Ratio of server accesses per underlying PRAM access.

- **Depth blowup:** Number of parallel steps to support a single batch of requests.

- Local Space: Space per checker. This talk: O(1) words/ $O(\lambda)$  bits.

- Server Space: Server storage size. This talk: O(N) words.

- Work blowup: Ratio of server accesses per underlying PRAM access.

- **Depth blowup:** Number of parallel steps to support a single batch of requests.

#### **Our Results**

bound of  $\Omega(\log N/\log \log N)$  known for special cases.

[Blum-Evans-Gemmel-Kannan-Naor '91]

• For RAM setting, the best constructions have  $O(\log N)$  work blow-up. Lower

#### **Our Results**

bound of  $\Omega(\log N/\log \log N)$  known for special cases.

[Blum-Evans-Gemmel-Kannan-Naor '91]

#### • For RAM setting, the best constructions have $O(\log N)$ work blow-up. Lower

[Dwork-Naor-Rothblum-Vaikuntanathan '09]

#### **Our Results**

bound of  $\Omega(\log N/\log \log N)$  known for special cases.

• For RAM setting, the best constructions have  $O(\log N)$  work blow-up. Lower

- bound of  $\Omega(\log N/\log \log N)$  known for special cases.

- up by serialising the algorithm. But  $O(m \log N)$  depth blowup.

• For RAM setting, the best constructions have  $O(\log N)$  work blow-up. Lower

• Immediately gives: *m*-CPU PRAM memory checker with  $O(\log N)$  work blow-

- For RAM setting, the best constructions have  $O(\log N)$  work blow-up. Lower bound of  $\Omega(\log N/\log \log N)$  known for special cases.

- Immediately gives: *m*-CPU PRAM memory checker with  $O(\log N)$  work blow-up by serialising the algorithm. **But**  $O(m \log N)$  depth blowup.

- We show how to also obtain  $O(\log N)$  <u>depth</u>.

- For RAM setting, the best constructions have  $O(\log N)$  work blow-up. Lower bound of  $\Omega(\log N/\log \log N)$  known for special cases.

- Immediately gives: *m*-CPU PRAM memory checker with  $O(\log N)$  work blow-up by serialising the algorithm. **But**  $O(m \log N)$  depth blowup.

- We show how to also obtain  $O(\log N)$  <u>depth</u>.

**Theorem 1.** Assuming <u>OWFs</u>, there exists a memory checking protocol for PRAM programs with  $O(\log N)$  worst-case work and <u>depth</u> blowup.

- bound of  $\Omega(\log N/\log \log N)$  known for special cases.

- up by serialising the algorithm. But  $O(m \log N)$  depth blowup.

- We show how to also obtain  $O(\log N)$  <u>depth</u>.

Theorem 1. Assuming OWFs, there exists a memory checking protocol for PRAM programs with  $O(\log N)$  worst-case work and depth blowup.

• For RAM setting, the best constructions have  $O(\log N)$  work blow-up. Lower

• Immediately gives: m-CPU PRAM memory checker with  $O(\log N)$  work blow-

Assumption is minimal [Naor-Rothblum '05]

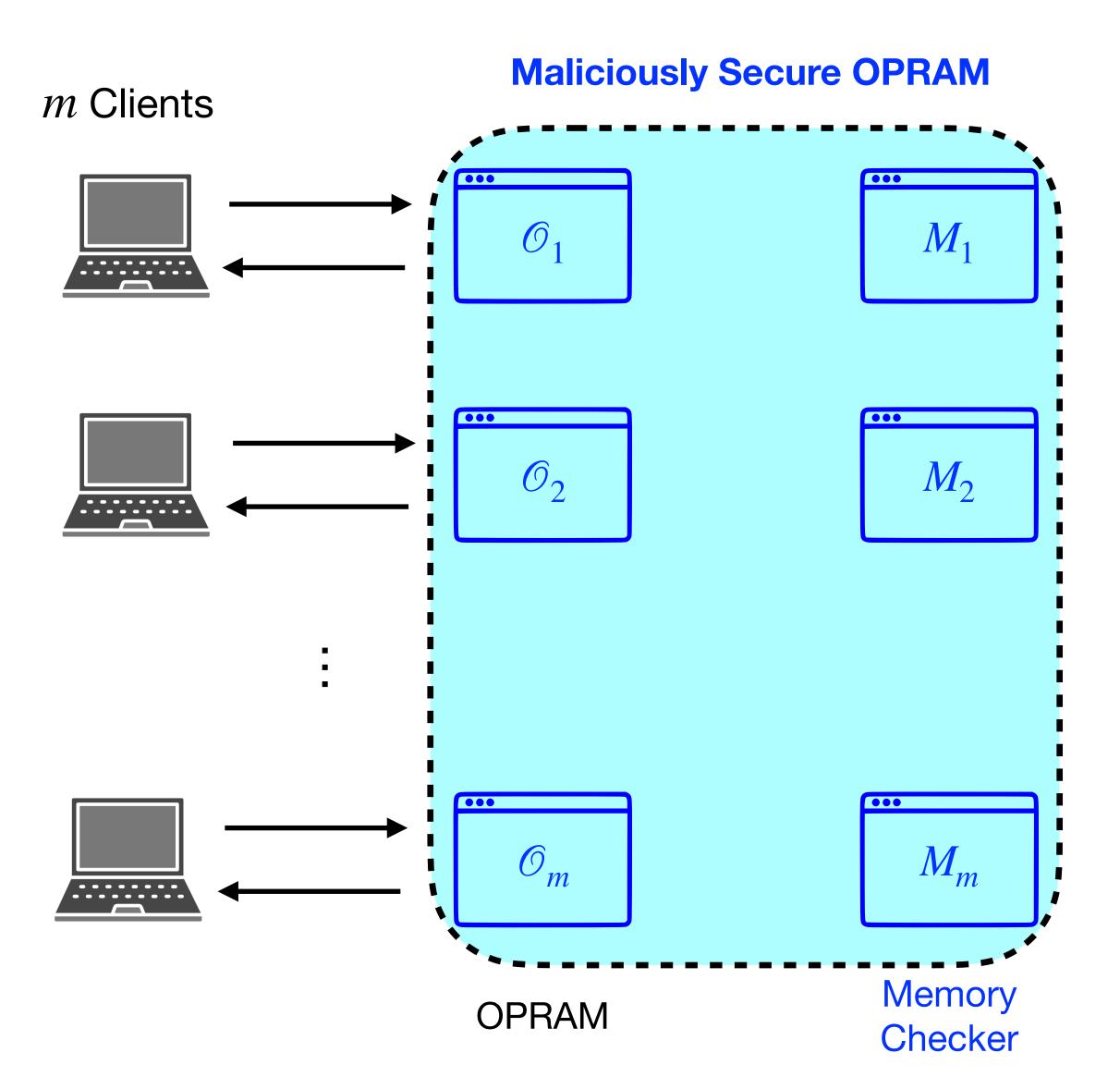

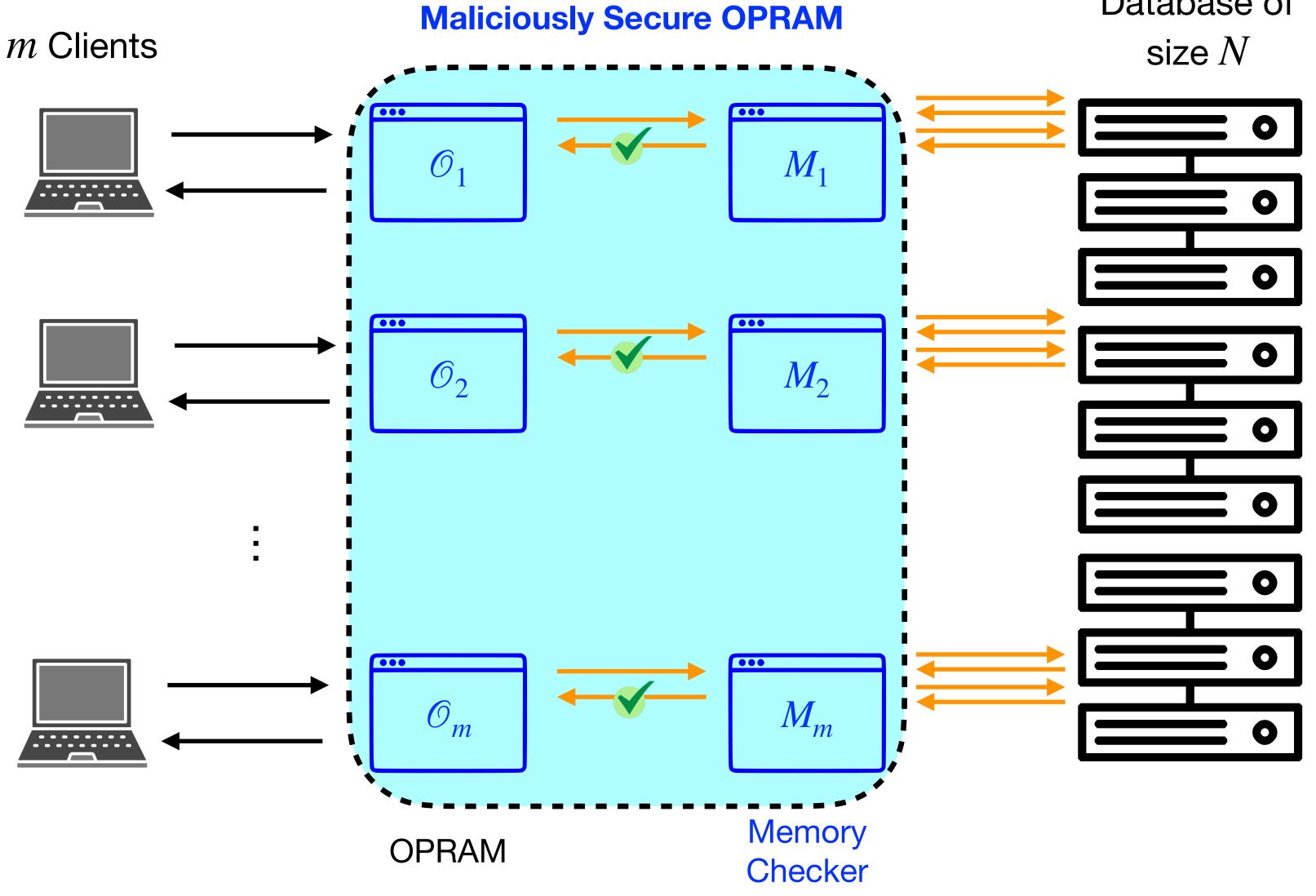

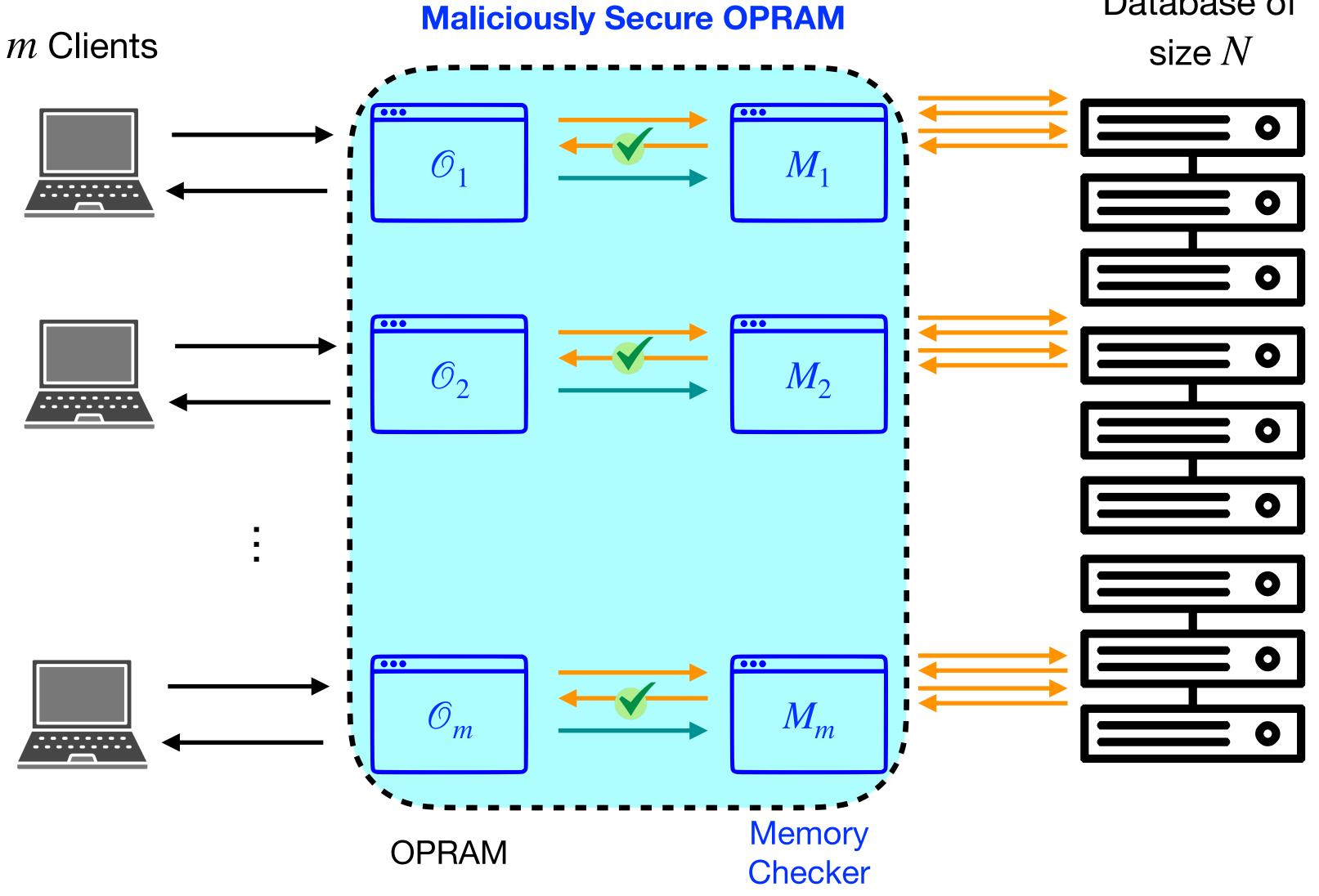

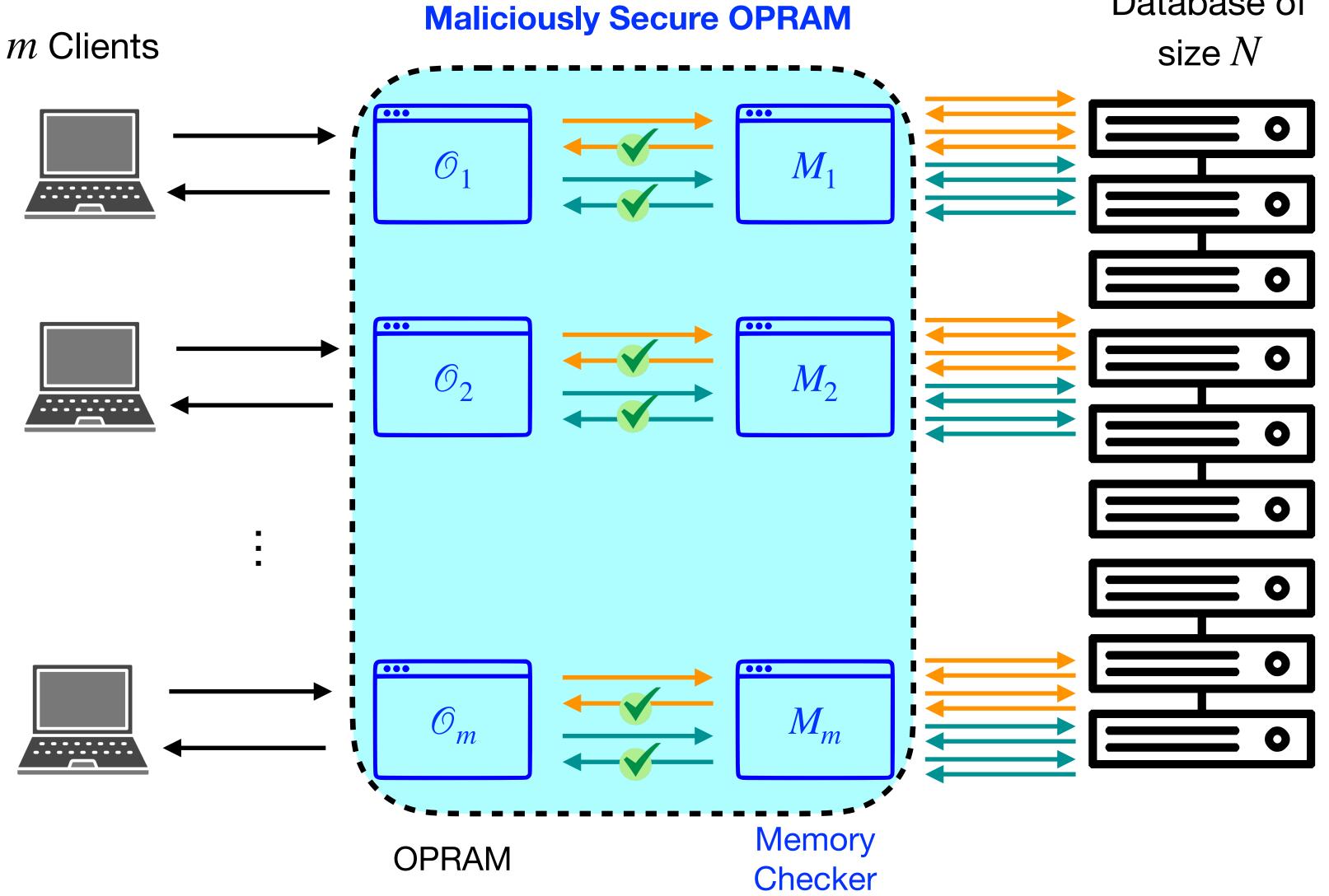

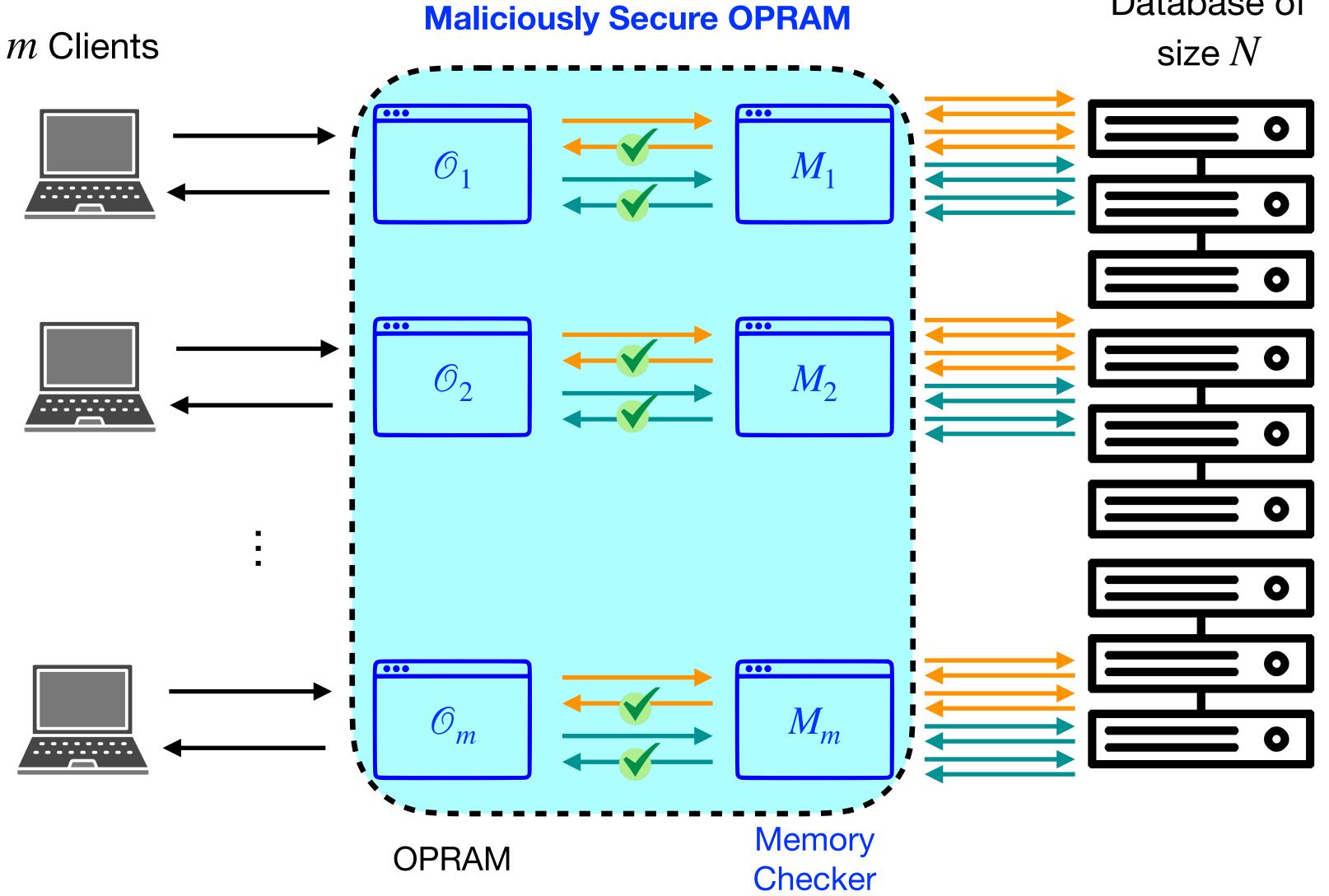

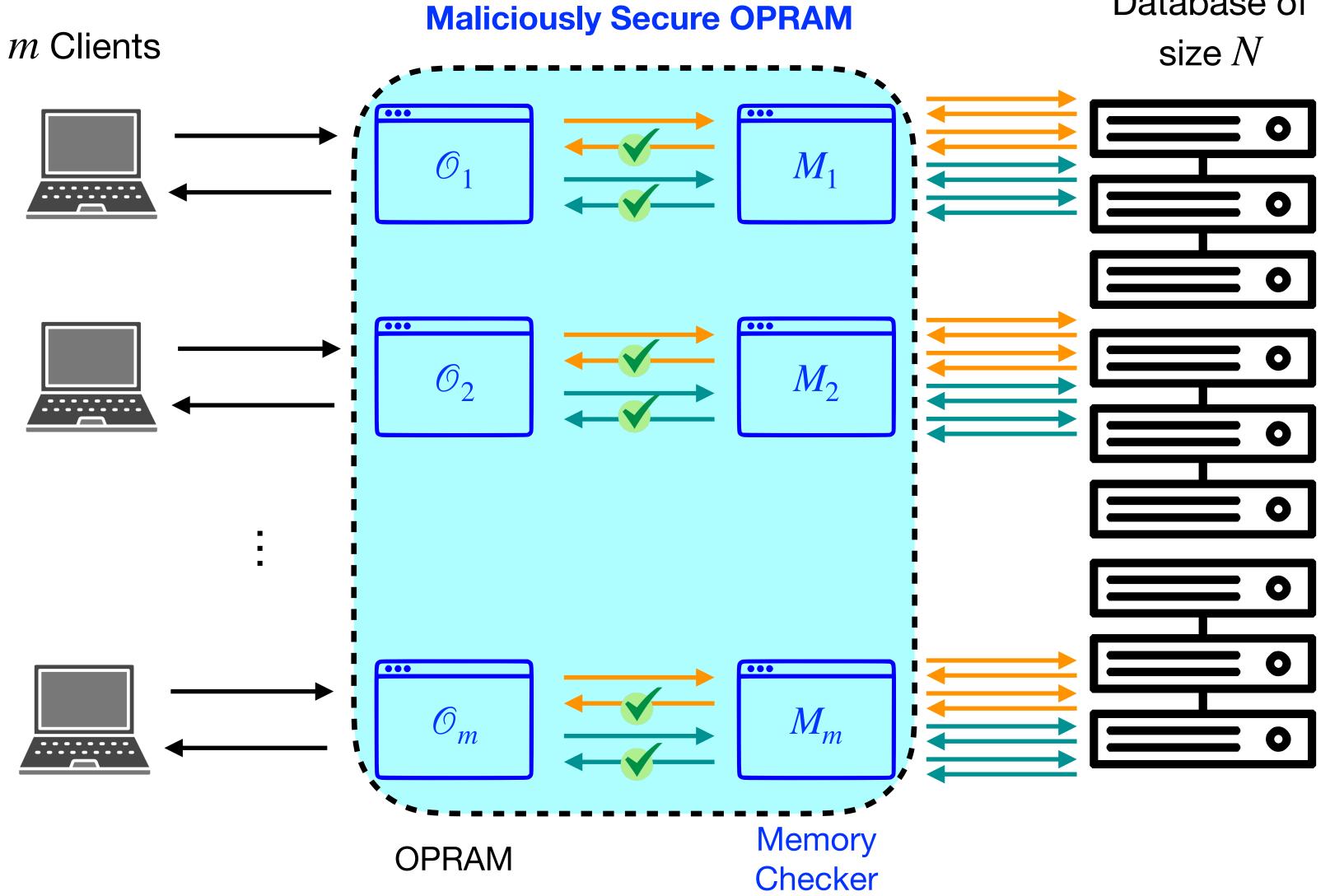

#### Oblivious Parallel RAMs (OPRAMs) are access-pattern hiding PRAM compilers. [Boyle-Chung-Pass '16]

- $O(\log N)$  blowup in both work and depth. Optimal!

Oblivious Parallel RAMs (OPRAMs) are access-pattern hiding PRAM compilers. [Boyle-Chung-Pass '16]

A recent work constructed an honest-but-curious OPRAM constructions with [Asharov-Komargodski-Lin-Peserico-Shi '22]

- Oblivious Parallel RAMs (OPRAMs) are access-pattern hiding PRAM compilers.

[Boyle-Chung-Pass '16]

- A recent work constructed an **honest-but-curious** OPRAM constructions with  $O(\log N)$  blowup in both **work** and **depth.** Optimal! [Asharov-Komargodski-Lin-Peserico-Shi '22]

- We obtain the <u>first</u> construction of maliciously secure OPRAM with polylogarithmic overhead.

- Oblivious Parallel RAMs (OPRAMs) are access-pattern hiding PRAM compilers. [Boyle-Chung-Pass '16]

- A recent work constructed an honest-but-curious OPRAM constructions with [Asharov-Komargodski- $O(\log N)$  blowup in both work and depth. Optimal! Lin-Peserico-Shi '22]

- We obtain the <u>first</u> construction of maliciously secure OPRAM with polylogarithmic overhead.

**OPRAM** compiler with  $O(\log^2 N)$  work and depth blowup\*.

**Theorem 2.** Assuming OWFs, there exists an maliciously secure

work and depth blowup.

work and depth blowup.

Query phase: Answers can be wrong! Repeat until clients say done.

work and depth blowup.

**Query phase:** Answers can be wrong! Repeat until clients say done.

work and depth blowup.

**Query phase:** Answers can be wrong! Repeat until clients say done.

#### **Theorem 3.** Assuming OWFs, there exists an <u>offline</u> memory checking protocol for PRAM programs with O(1) amortised

Verification phase: Reports if <u>all</u> correct or some mistake.

work and depth blowup.

#### checking protocol for PRAM programs with O/ work and depth b

Checks if any mistake happened after a large batch of concurrent requests

Theorem 3. Assuming OWFs, there exists an offline memory amortised

work and depth blowup.

Theorem 3. Assuming OWFs, there exists an offline memory checking protocol for PRAM programs with O(1) amortised work and depth blowup.

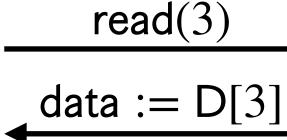

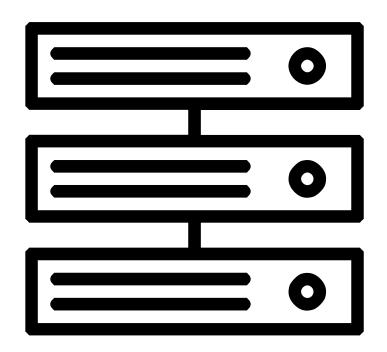

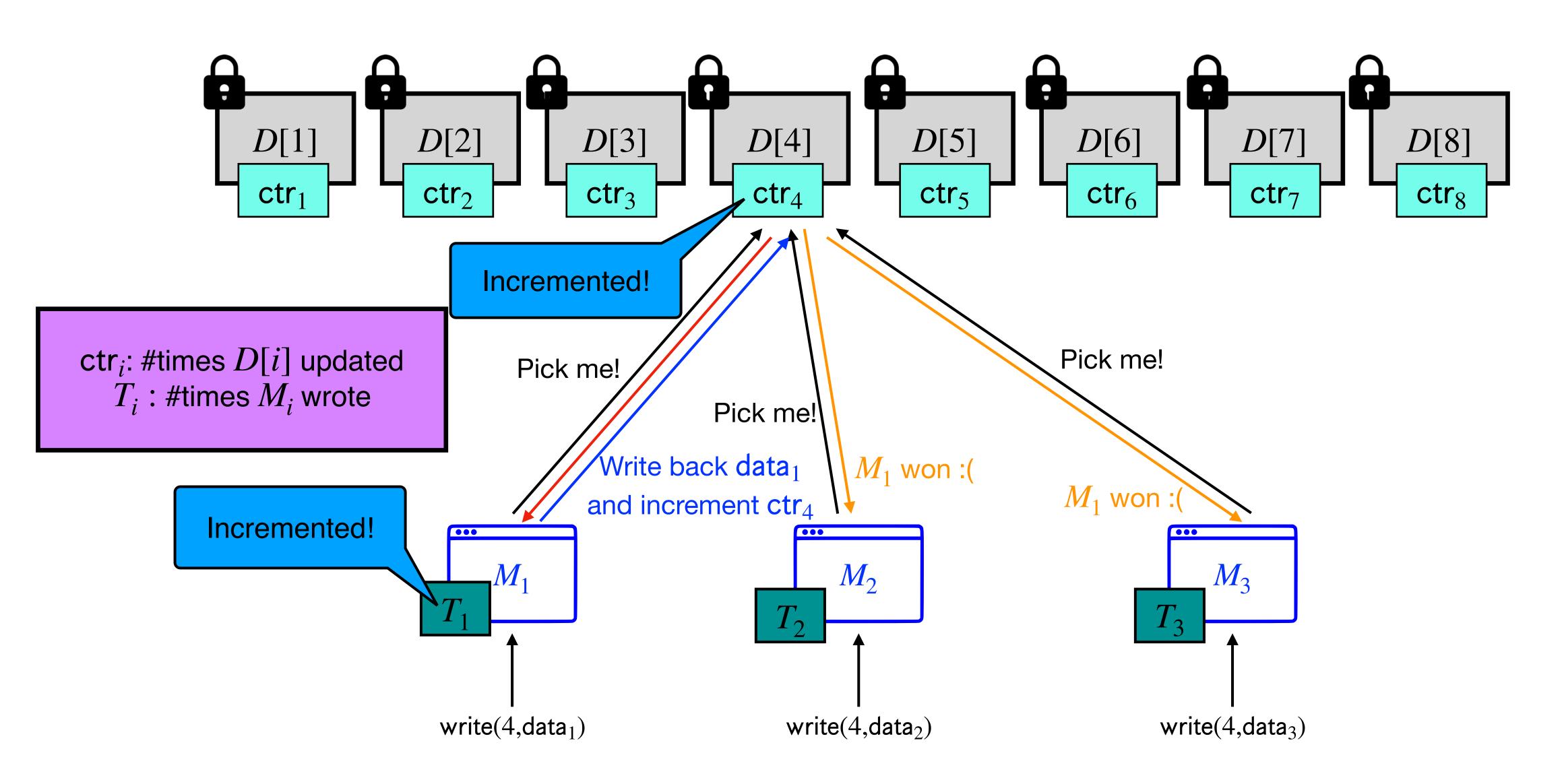

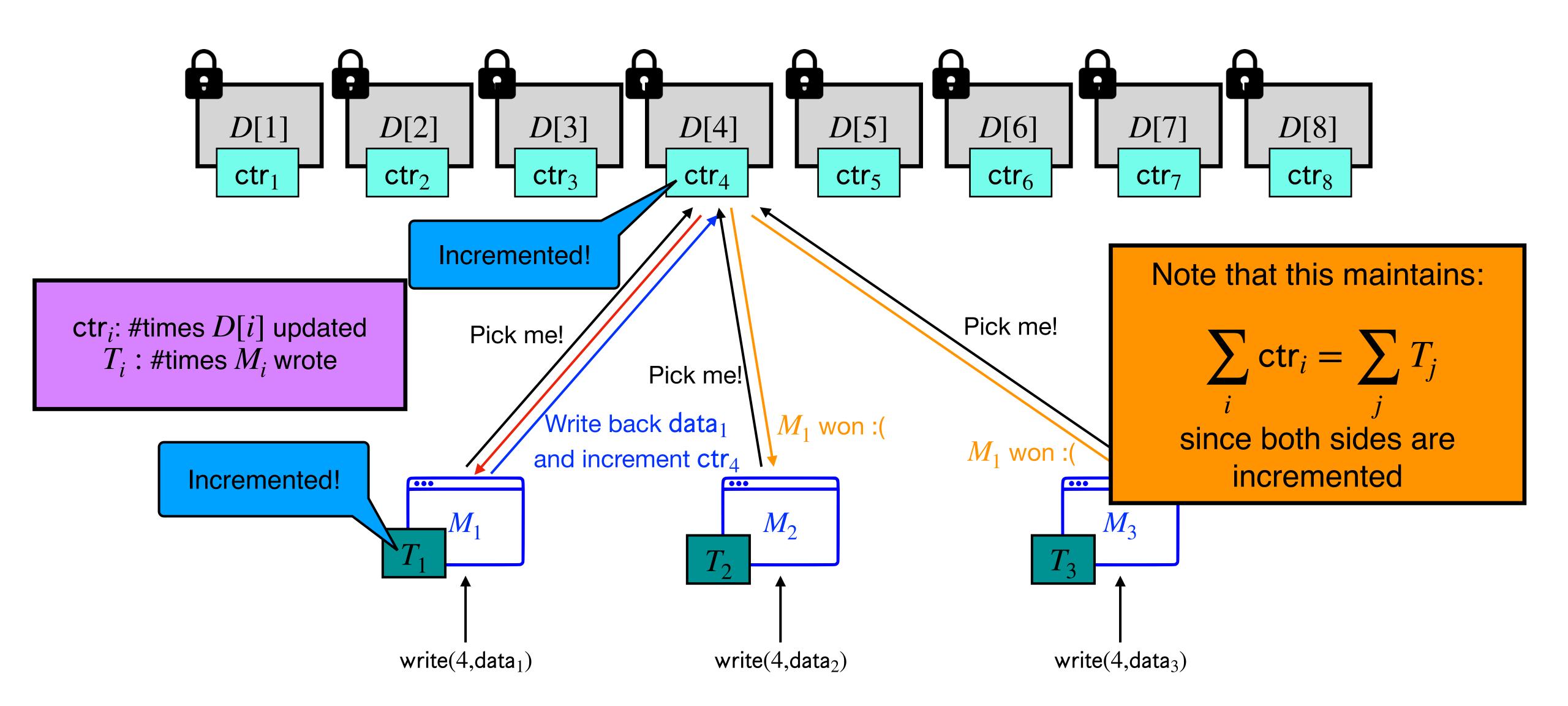

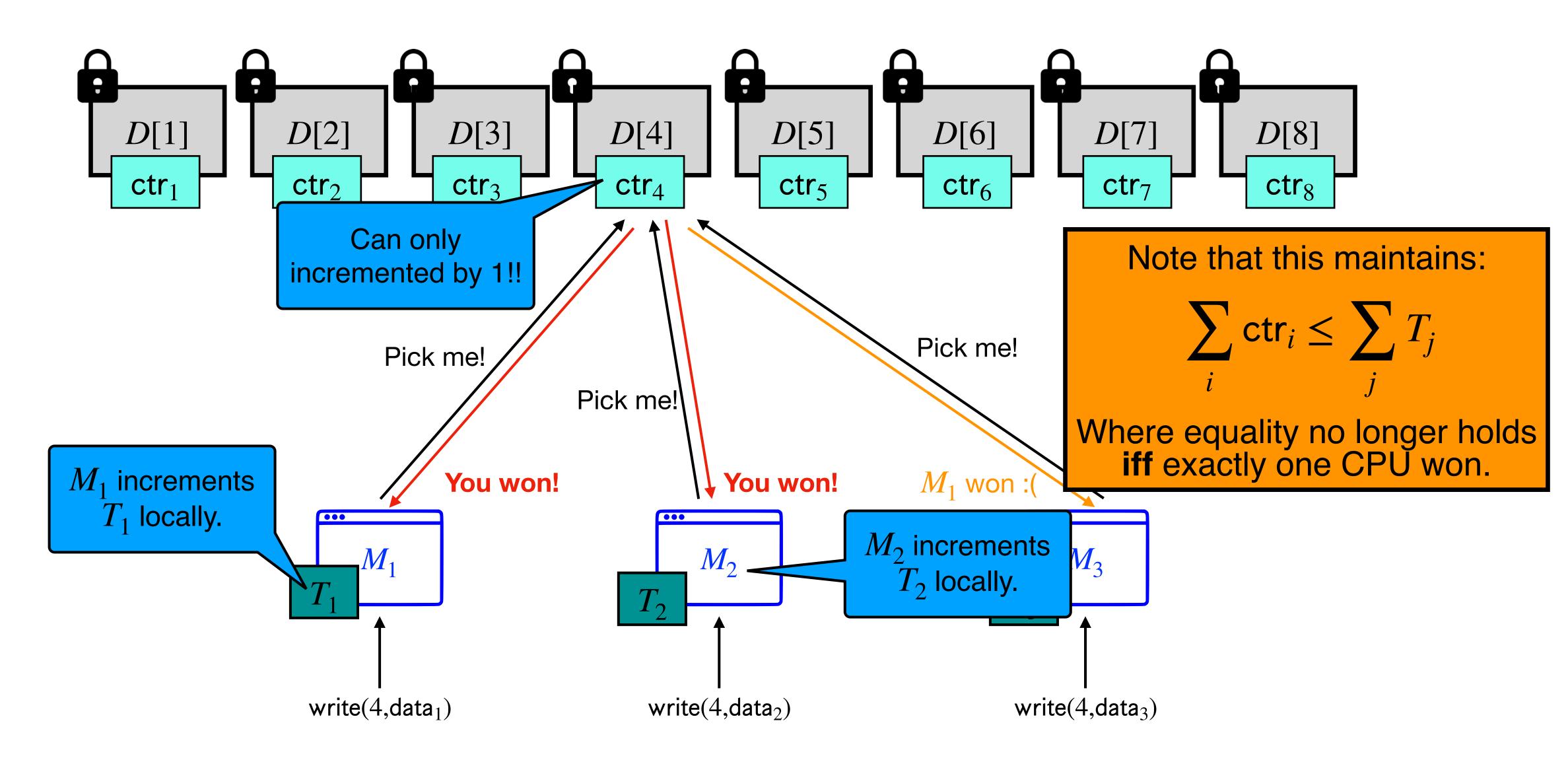

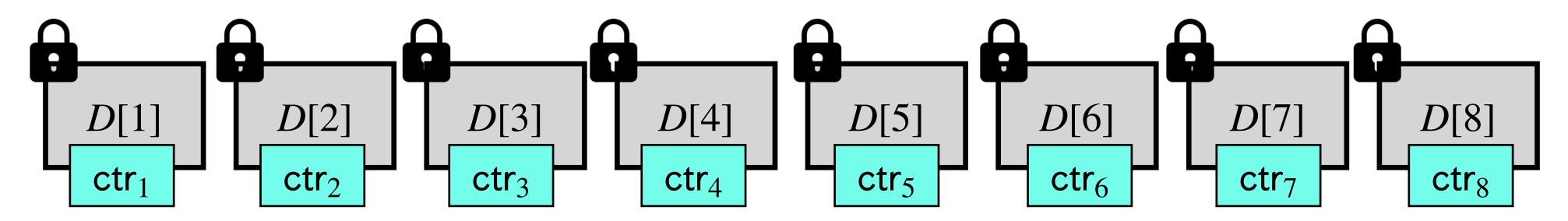

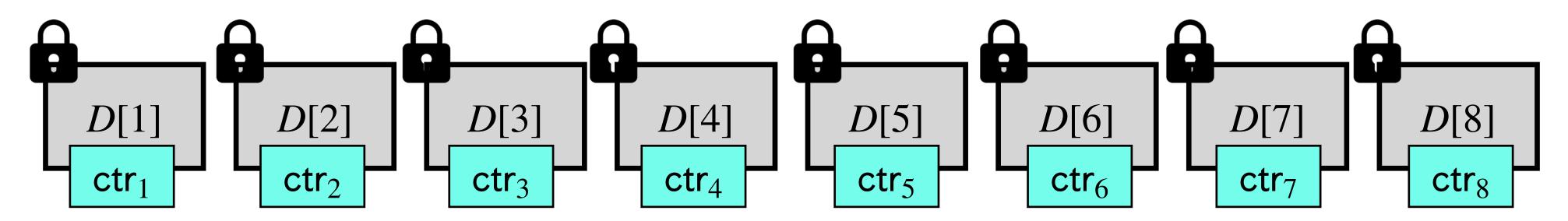

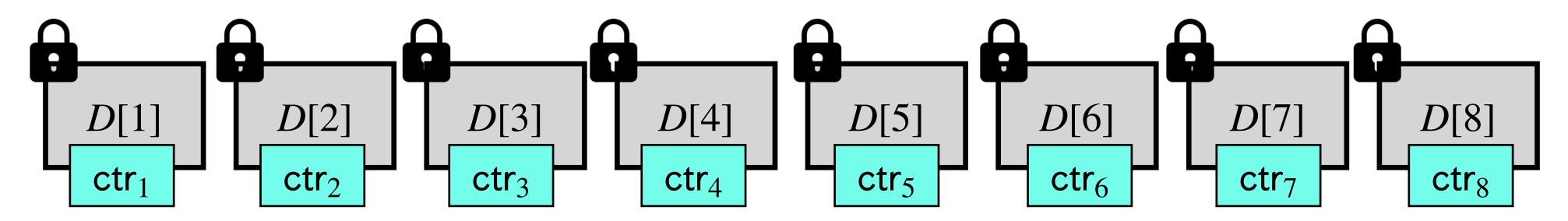

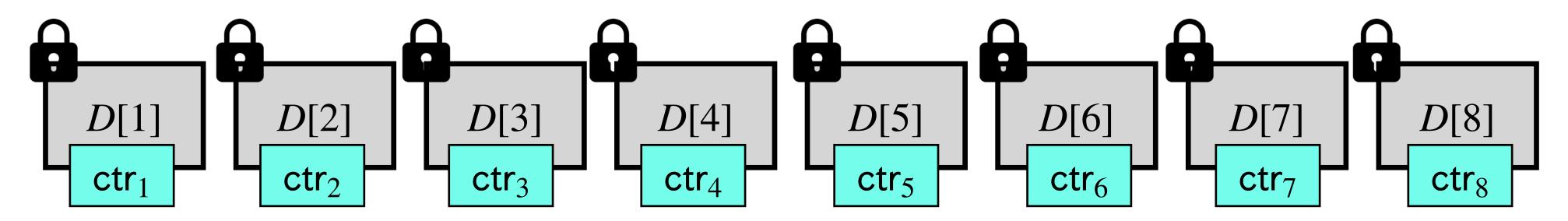

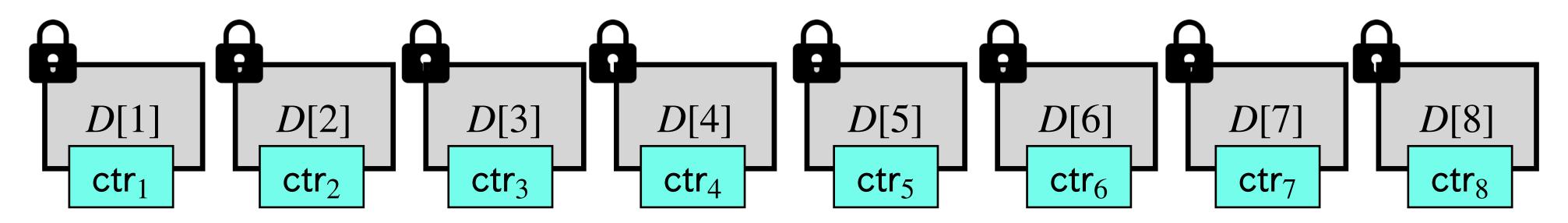

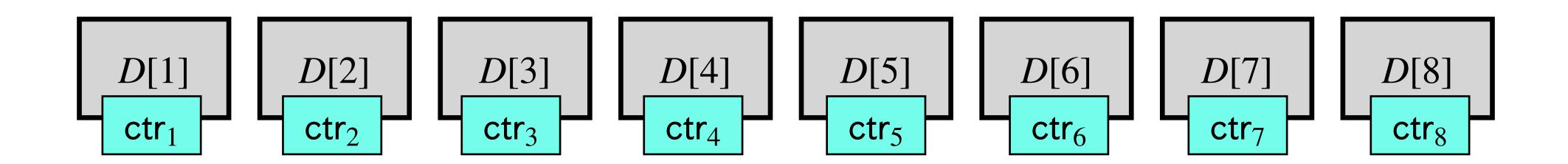

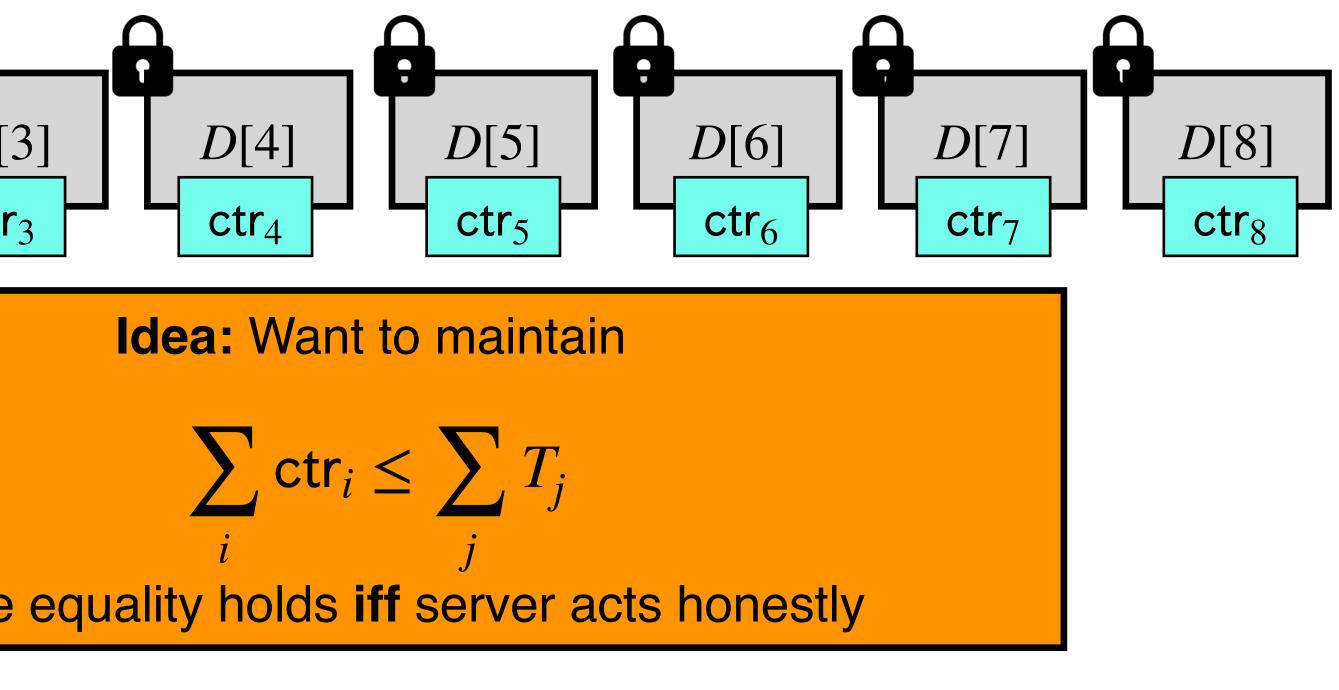

• Idea: Adapt the counting technique from a previous work [M.-Vafa '23]

- Idea: Adapt the counting technique from a previous work [M.-Vafa '23]

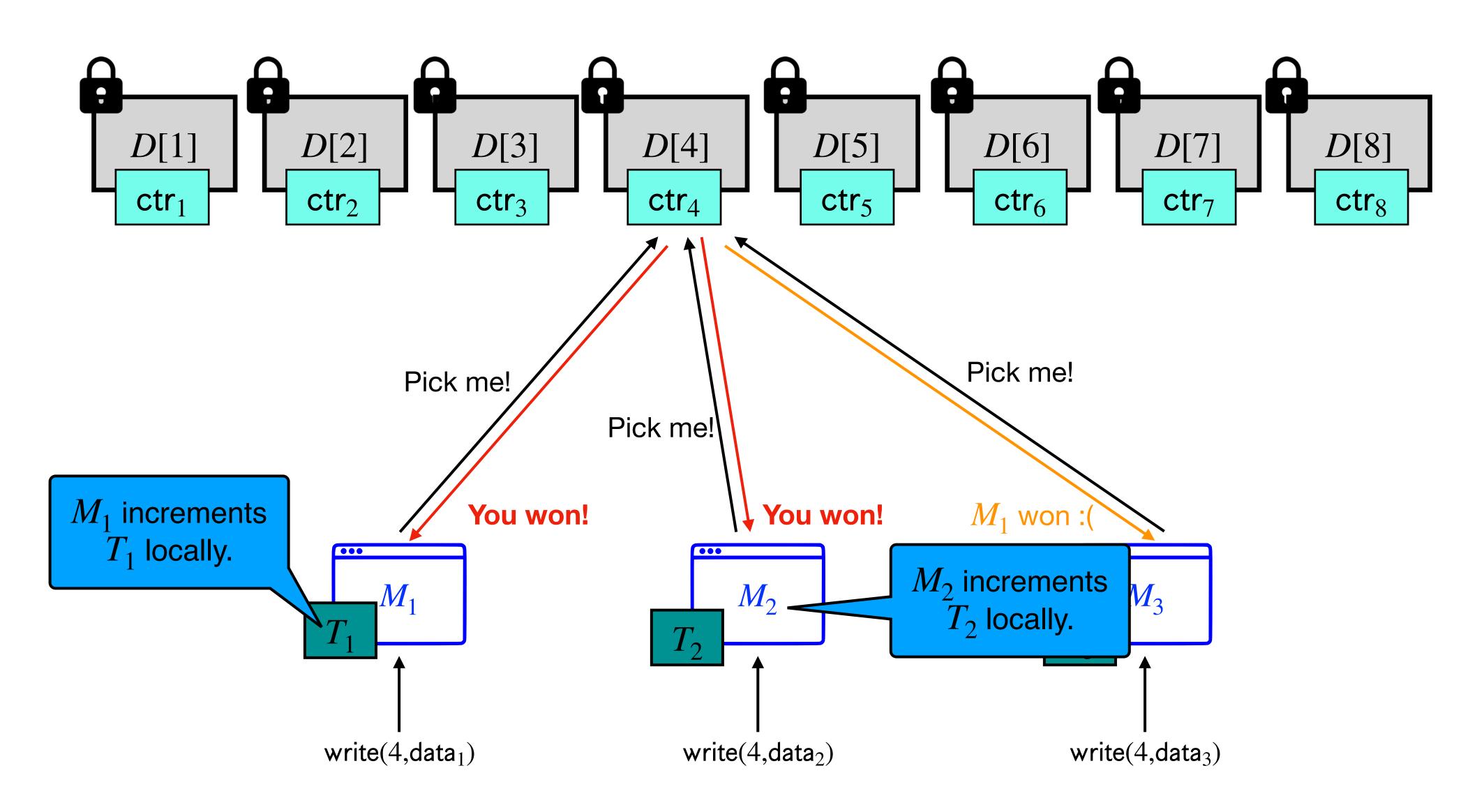

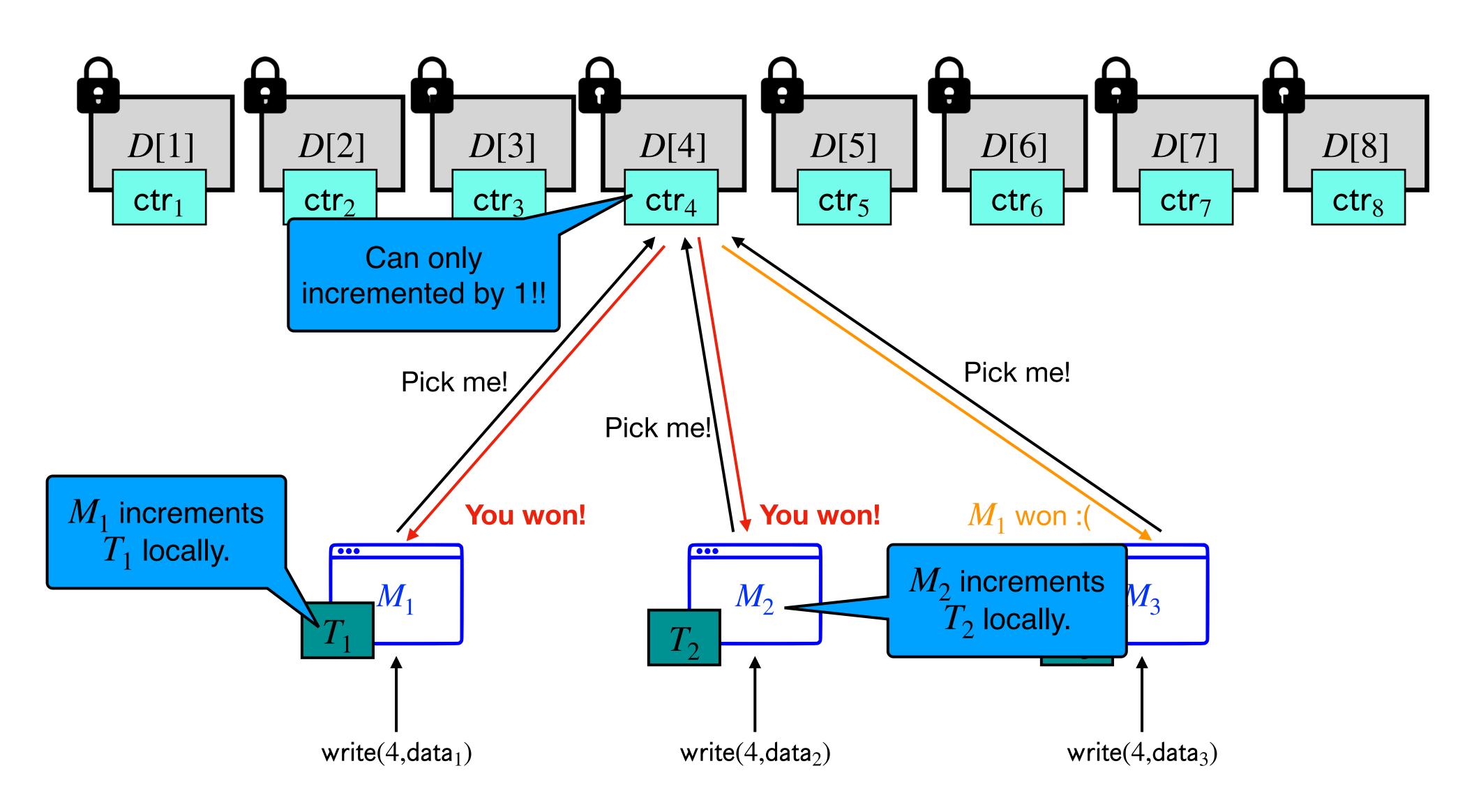

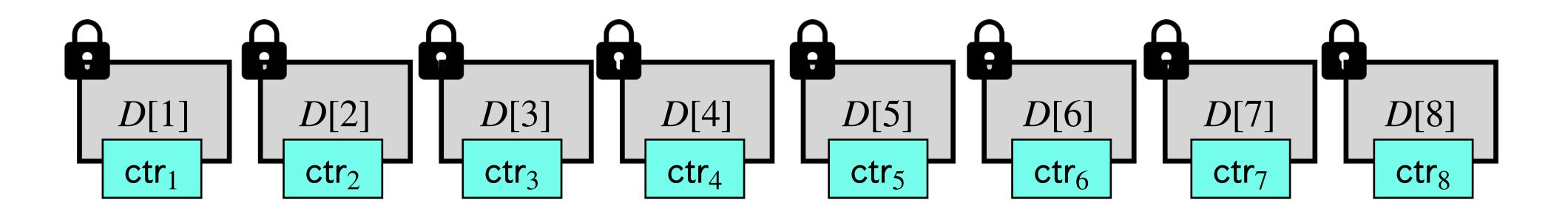

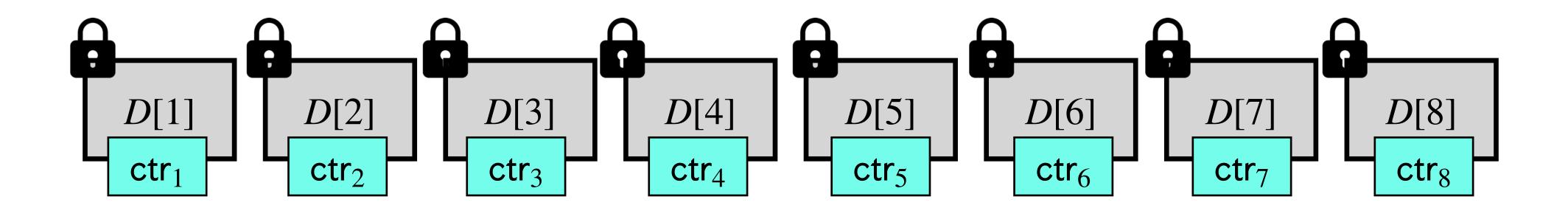

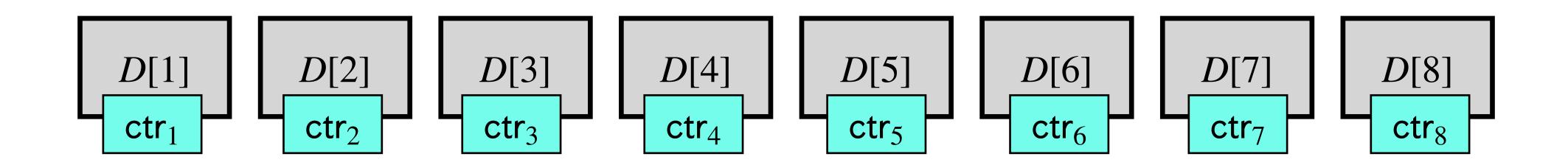

- Memory checkers maintain local counters  $T_i$  of the number of updates.

- Idea: Adapt the counting technique from a previous work [M.-Vafa '23]

- Memory checkers maintain local counters  $T_i$  of the number of updates.

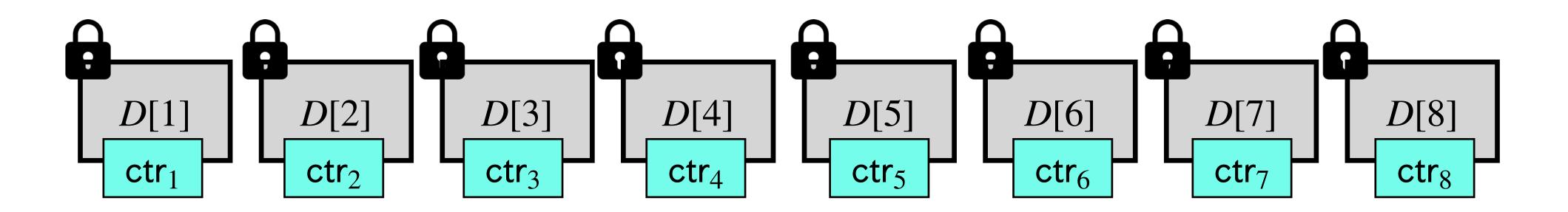

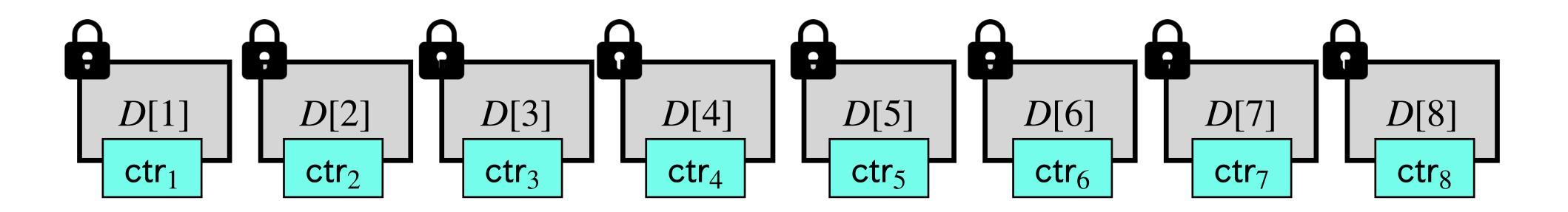

- Every database entry is tagged with counters ctr<sub>i</sub>

**Theorem 3.** Assuming OWFs, there exists an <u>offline</u> memory checking protocol for PRAM programs with O(1) amortised **work** and **depth** blowup.

- Idea: Adapt the counting technique from a previous work [M.-Vafa '23]

- Memory checkers maintain local counters  $T_i$  of the number of updates.

- Every database entry is tagged with counters ctr<sub>i</sub>

Verification phase: Check if  $\sum$

$$\operatorname{ctr}_i = \sum_j T_j.$$

# **New: Offline-Checking for PRAMs**

ctr<sub>*i*</sub>: #times *D*[*i*] updated  $T_i$ : #times  $M_i$  wrote

# **New: Offline-Checking for PRAMs**

#### **New:** Offline-Checking for PRAMs *D*[2] *D*[3] *D*[4] *D*[5] *D*[6] *D*[7] *D*[8] D[1]ctr<sub>8</sub> ctr<sub>1</sub> ctr<sub>2</sub> ctr<sub>4</sub> ctr<sub>7</sub> ctr<sub>3</sub> $ctr_5$ ctr<sub>6</sub> $ctr_i$ : #times D[i] updated Pick me! Pick me! $T_i$ : #times $M_i$ wrote Pick me! $M_1$ won :( You won! $M_1$ won $M_3$ $M_2$ $M_1$ T **1**2 13 I $write(4, data_1)$

#### **New:** Offline-Checking for PRAMs *D*[2] *D*[3] *D*[4] *D*[5] *D*[6] *D*[7] *D*[8] *D*[1] ctr<sub>8</sub> ctr<sub>1</sub> ctr<sub>2</sub> ctr<sub>4</sub> $ctr_7$ ctr<sub>3</sub> $ctr_5$ $ctr_6$ $ctr_i$ : #times D[i] updated Pick me! Pick me! $T_i$ : #times $M_i$ wrote Pick me! Write back data<sub>1</sub> $M_1$ won :( $M_1$ won : and increment ctr<sub>4</sub> $M_3$ $M_2$ $M_1$ T 12 **1**3 I $write(4, data_1)$

# New: Offline-Checking for PRAMs

# New: Offline-Checking for PRAMs

# **Open Problems**

# **Open Problems**

• Can we obtain a statistically secure with O(1) amortised overhead?

• Can we obtain a statistically secure offline memory checker for CRCW programs

- Can we obtain a **statistically secure** offline memory checker for CRCW programs with O(1) amortised overhead?

- Known for single RAM setting, and we show for PRAM setting without concurrent read/writes.

- Can we obtain a **statistically secure** offline memory checker for CRCW programs with O(1) amortised overhead?

- Known for single RAM setting, and we show for PRAM setting without concurrent read/writes.

- Can we use these memory checkers to obtain an **optimal maliciously secure OPRAM** with  $O(\log N)$  work and depth blow-up?

- Can we obtain a **statistically secure** offline memory checker for CRCW programs with O(1) amortised overhead?

- Known for single RAM setting, and we show for PRAM setting without concurrent read/writes.

- Can we use these memory checkers to obtain an **optimal maliciously secure OPRAM** with  $O(\log N)$  work and depth blow-up?

- [M-Vafa '23] shows an  $O(\log N)$  maliciously secure ORAM construction by interleaving offline and online memory checking.

- Can we obtain a **statistically secure** offline memory checker for CRCW programs with O(1) amortised overhead?

- Known for single RAM setting, and we show for PRAM setting without concurrent read/writes.

- Can we use these memory checkers to obtain an **optimal maliciously secure OPRAM** with  $O(\log N)$  work and depth blow-up?

- [M-Vafa '23] shows an  $O(\log N)$  maliciously secure ORAM construction by interleaving offline and online memory checking.

- Can we do the same?

### **Bonus Slides**

*m* Clients

*m* Clients

Database of size N

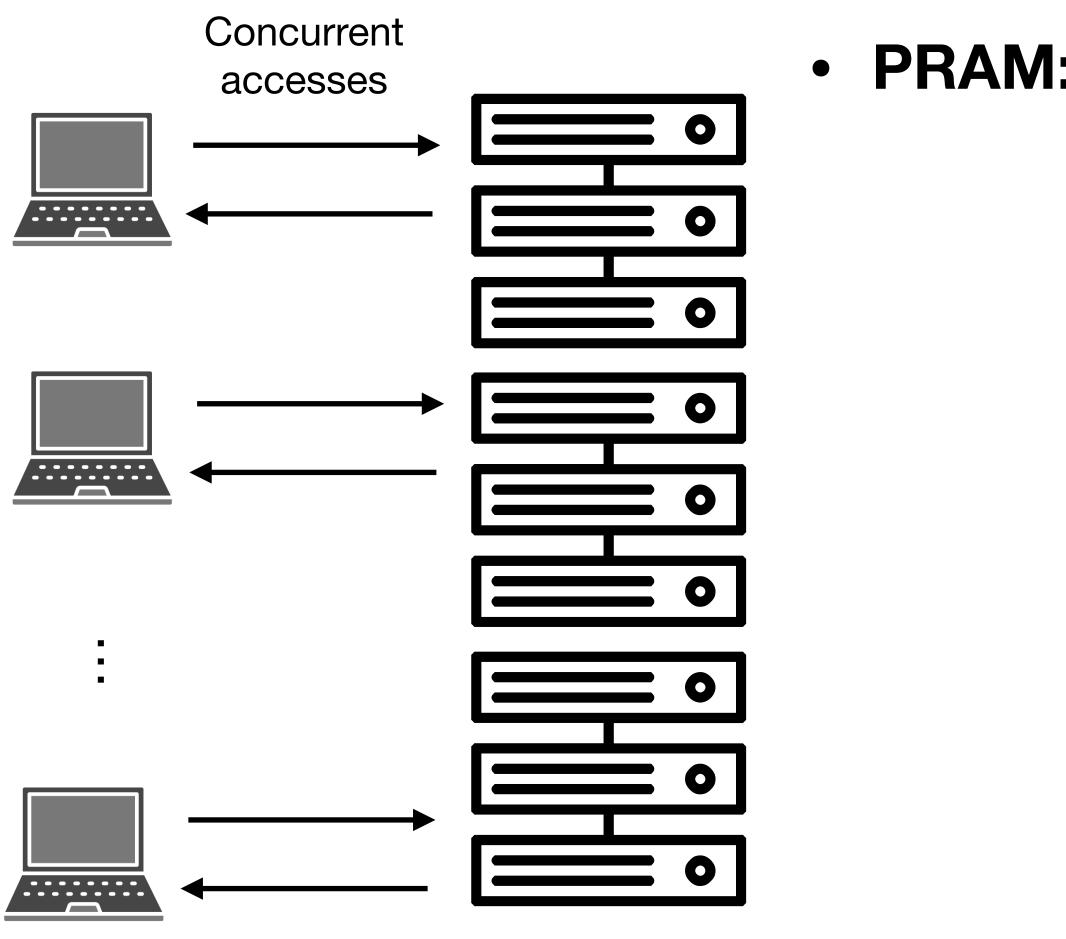

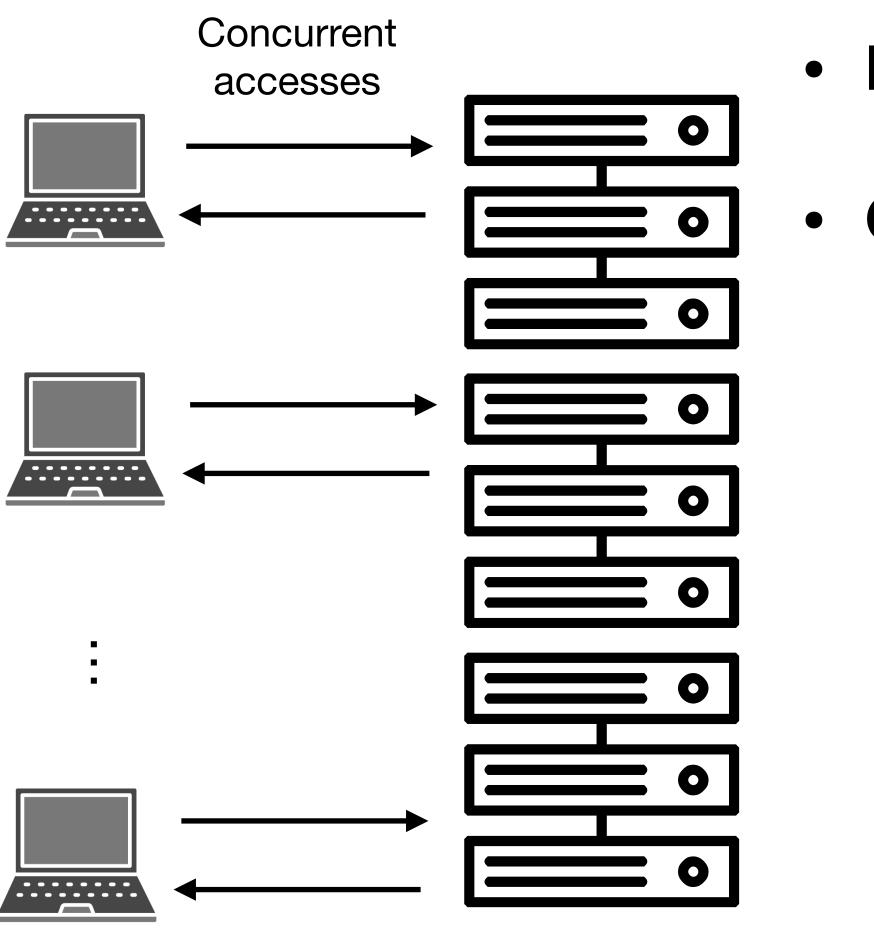

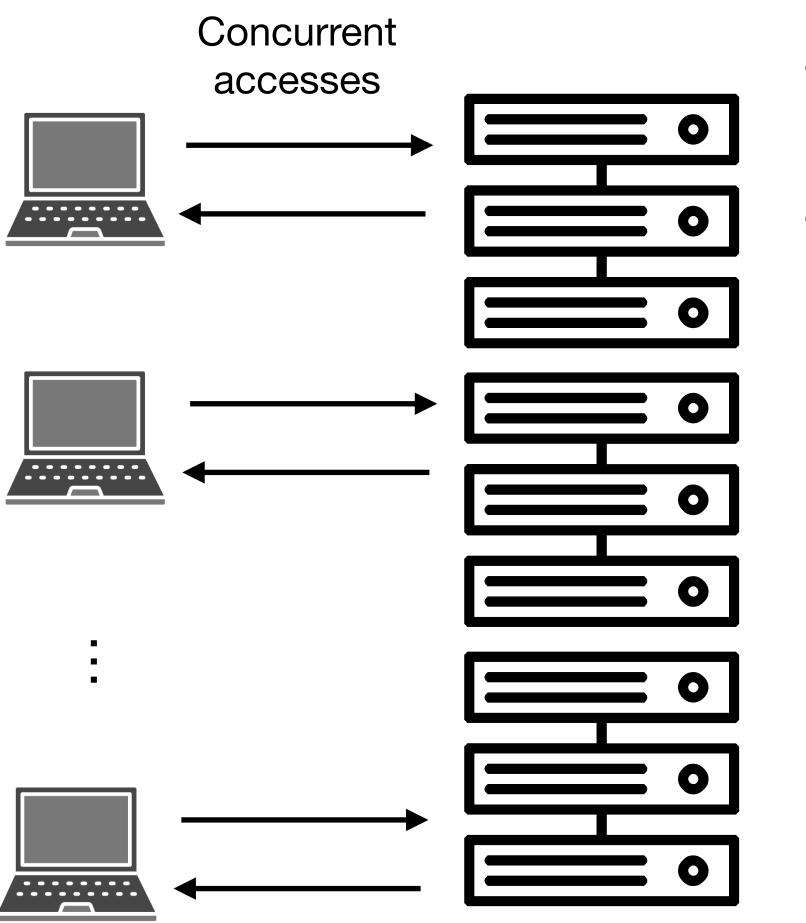

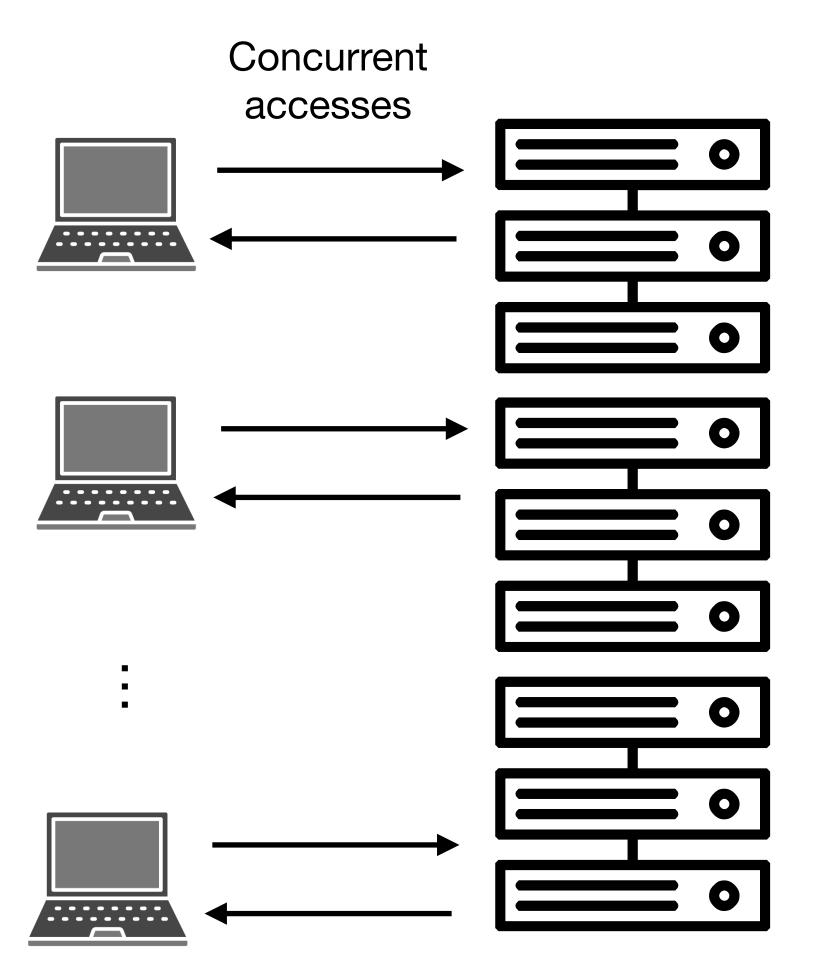

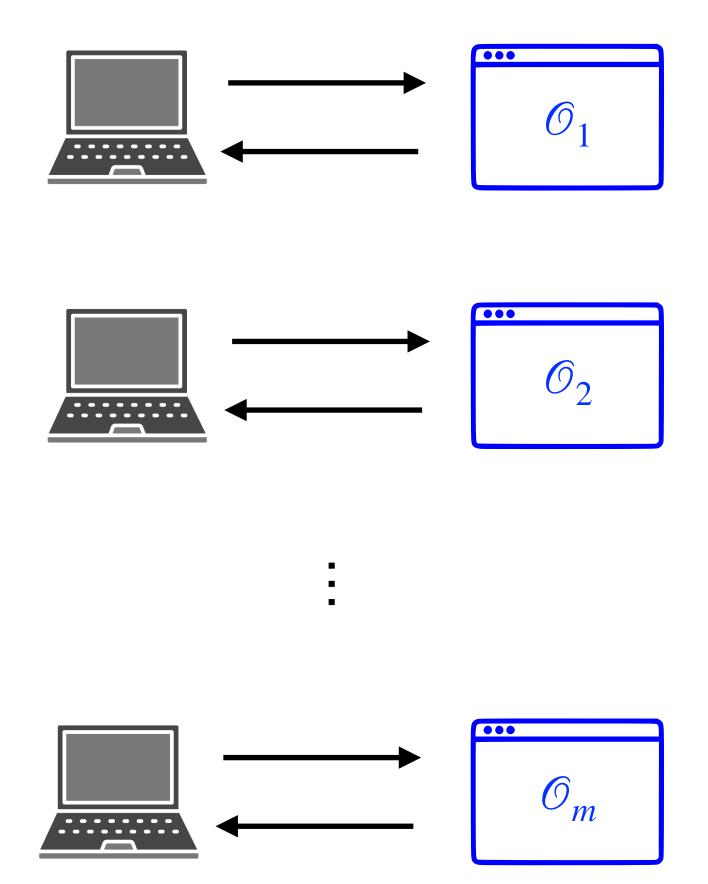

• **PRAM:** Multiple CPUs accessing shared memory

*m* Clients

Database of size N

**PRAM:** Multiple CPUs accessing shared memory

*m* Clients

Database of size N

**PRAM:** Multiple CPUs accessing shared memory

- **PRAM:** Multiple CPUs accessing shared memory

- CRCW Model: <u>Concurrent</u> <u>Read</u> <u>Concurrent</u> <u>Write</u>

*m* Clients

Database of size N

- **PRAM:** Multiple CPUs accessing shared memory

- CRCW Model: Concurrent Read Concurrent Write Concurrent reads to any location are allowed.

*m* Clients

Database of size N

- **PRAM:** Multiple CPUs accessing shared memory

- CRCW Model: <u>Concurrent Read</u> <u>Concurrent Write</u> Concurrent reads to any location are allowed.

*m* Clients

- **PRAM:** Multiple CPUs accessing shared memory

- CRCW Model: <u>Concurrent Read</u> <u>Concurrent Write</u> Concurrent reads to any location are allowed.

- **PRAM:** Multiple CPUs accessing shared memory

- CRCW Model: Concurrent Read Concurrent Write • Concurrent reads to any location are allowed. Concurrent writes to any location are <u>arbitrarily tie-</u> broken.

- **PRAM:** Multiple CPUs accessing shared memory

- CRCW Model: Concurrent Read Concurrent Write Concurrent reads to any location are allowed. Concurrent writes to any location are <u>arbitrarily tie-</u> broken.

*m* Clients

- **PRAM:** Multiple CPUs accessing shared memory

- CRCW Model: Concurrent Read Concurrent Write Concurrent reads to any location are allowed. Concurrent writes to any location are <u>arbitrarily tie-</u> broken.

*m* Clients

- **PRAM:** Multiple CPUs accessing shared memory

- CRCW Model: Concurrent Read Concurrent Write • Concurrent reads to any location are allowed. • **Concurrent writes** to any location are <u>arbitrarily tie-</u> broken.

*m* Clients

- **PRAM:** Multiple CPUs accessing shared memory

- CRCW Model: Concurrent Read Concurrent Write Concurrent reads to any location are allowed. Concurrent writes to any location are <u>arbitrarily tie-</u> broken.

- Note: Not every client has to perform an operation.

*m* Clients

*m* Clients

- **PRAM:** Multiple CPUs accessing shared memory

- CRCW Model: Concurrent Read Concurrent Write Concurrent reads to any location are allowed. Concurrent writes to any location are <u>arbitrarily tie-</u>

- Note: Not every client has to perform an operation.

- **Two efficiency metrics for PRAM algorithms:**

Database of size N

*m* Clients

- **PRAM:** Multiple CPUs accessing shared memory

- CRCW Model: <u>Concurrent</u> <u>Read</u> <u>Concurrent</u> <u>Write</u> Concurrent reads to any location are allowed. Concurrent writes to any location are <u>arbitrarily tie-</u>

- Note: Not every client has to perform an operation.

### **Two efficiency metrics for PRAM algorithms:**

Work: Number of read/write operations

- **PRAM:** Multiple CPUs accessing shared memory

- CRCW Model: <u>Concurrent</u> <u>Read</u> <u>Concurrent</u> <u>Write</u> Concurrent reads to any location are allowed. Concurrent writes to any location are <u>arbitrarily tie-</u>

- Note: Not every client has to perform an operation.

#### **Two efficiency metrics for PRAM algorithms:**

- Work: Number of read/write operations

- <u>Depth</u>: Number of parallel steps

#### *m* Clients

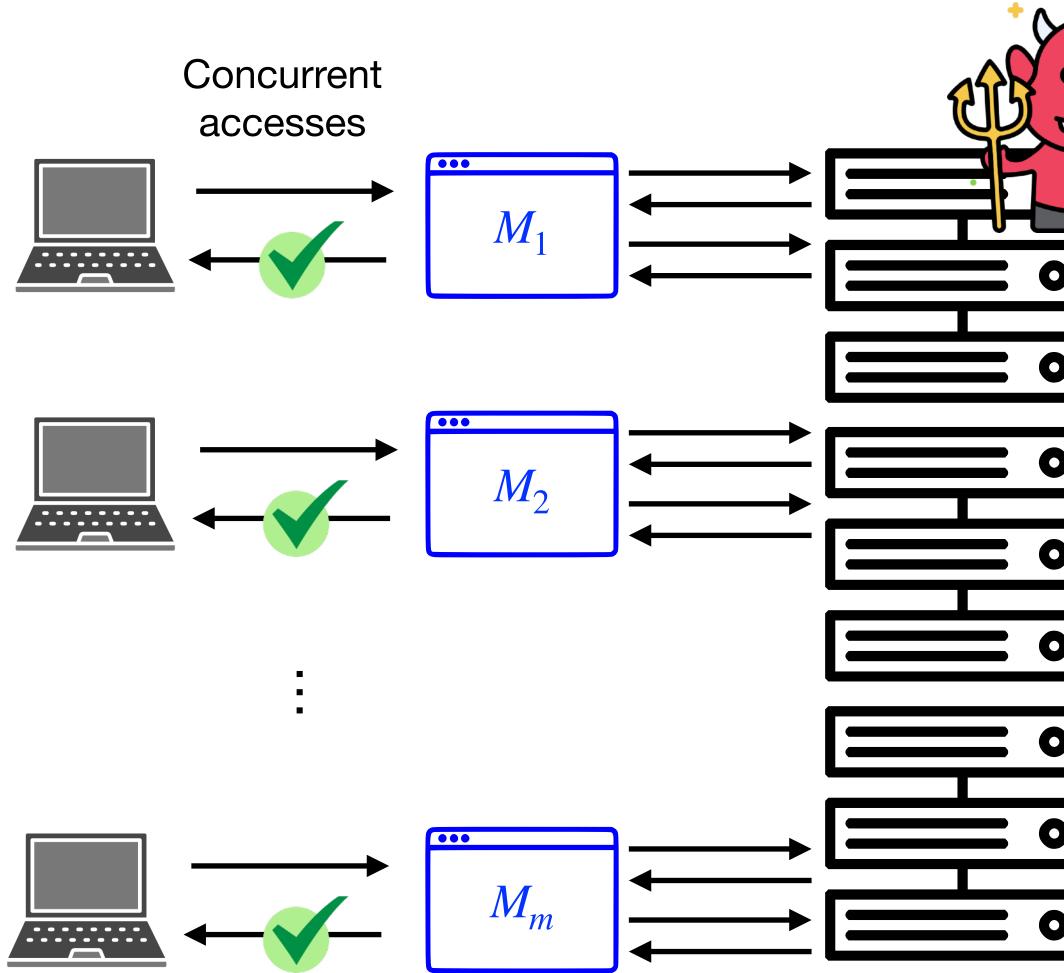

OPRAM

#### *m* Clients

Database of

MC ensures all responses to OPRAM are correct.

- MC ensures all responses to OPRAM are correct.

- Can invoke semi-honest security of **OPRAM!**

Database of

- MC ensures all responses to OPRAM are correct.

- Can invoke semihonest security of **OPRAM!**

**Blowup (work and depth):**

Database of

- MC ensures all responses to OPRAM are correct.

- Can invoke semihonest security of **OPRAM!**

**Blowup (work and depth):**

$\log N \times \log N = \log^2 N$

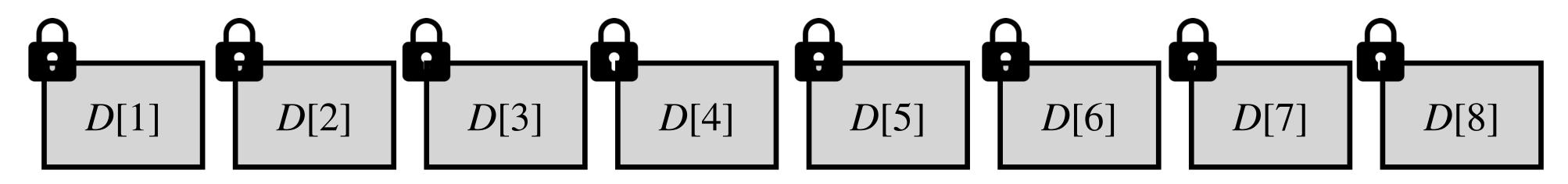

### **Offline-Checking for RAMs**

[Blum, Evans, Gemmel, Kannan, Naor '94], this construction is based on [M, Vafa `23]

### **Offline-Checking for RAMs**

[Blum, Evans, Gemmel, Kannan, Naor '94], this construction is based on [M, Vafa `23]

[Blum, Evans, Gemmel, Kannan, Naor '94], this construction is based on [M, Vafa 23]

[Blum, Evans, Gemmel, Kannan, Naor '94], this construction is based on [M, Vafa 23]

- Memory checker local stores a counter T initialised to 0.

[Blum, Evans, Gemmel, Kannan, Naor '94], this construction is based on [M, Vafa 23]

- Memory checker local stores a counter T initialised to 0.

- For every access to D[i], increment T locally, and increment  $ctr_i$ .

[Blum, Evans, Gemmel, Kannan, Naor '94], this construction is based on [M, Vafa 23]

- Memory checker local stores a counter T initialised to 0.

- For every access to D[i], increment T locally, and increment  $ctr_i$ .

- At the end, the memory checker iterates over the array and verifies  $\sum ctr_i = T$ .

[Blum, Evans, Gemmel, Kannan, Naor '94], this construction is based on [M, Vafa 23]

- For entry D[i], let  $ctr_i = number$  of times location i was

- Memory checker local stores a counter T initialised to 0.

- For every access to D[i], increment T locally, and increm

- At the end, the memory checker iterates over the array and verifies

Idea: Let  $t_i$  be the number of times D[i] was actually accessed.

$$\sum \operatorname{ctr}_i \leq \sum t_i = T$$

where equality holds iff there was no replay attack.

$$\sum \operatorname{ctr}_i = T.$$

- Each  $M_i$  keeps a local count  $T_i$ .

• As before: Initialise all entries with  $ctr_i = 0$  and authenticate all entries.

$write(4, data_1)$